## Problema

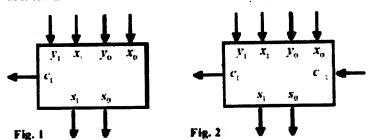

En la Fig. 1 se muestra el diagrama de bloques de un sumador binario de dos números de 2 bits. Las entradas al sumador son los dos bits de cada sumando  $(X=x_1x_0, Y=y_1y_0)$ . Las salidas son los dos bits de suma  $(s=s_1s_0)$  y el bit de arrastre  $(c_1)$ .

- A) (0.75 puntos) Obtenga la tabla de la verdad de las salidas (c<sub>1</sub>, s<sub>1</sub>, s<sub>0</sub>) del sumador de la Fig. 1 en función de las entradas (y<sub>1</sub>, y<sub>0</sub>, x<sub>1</sub>, x<sub>0</sub>).

- B) (1 punto) Obtenga las funciones lógicas simplificadas de las tres salidas (c<sub>1</sub>, s<sub>1</sub>, s<sub>0</sub>) del sumador de la Fig. 1 en función de las entradas (y<sub>1</sub>, y<sub>0</sub>, x<sub>1</sub>, x<sub>0</sub>). Emplee para ello mapas de Karnaugh.

- C) (0.75 puntos) A partir de las funciones lógicas calculadas en el apartado anterior, realizar el sumador binario de 2 bits mostrado en la Fig. 1 mediante un circuito combinacional de dos niveles (AND-OR).

- D) (1.5 puntos) Si al sumador binario de la Fig. 1 se le añade una nueva entrada, "bit de arrastre de la etapa anterior" (c<sub>1</sub>), se obtiene el sumador representado en la Fig. 2. Empleando módulos sumadores como el mostrado en la Fig.2, multiplexores y puertas lógicas, diseñe una ALU aritmética de 4 bits que realice las cinco operaciones siguientes sobre dos números A y B de 4 bits: suma (Z=A+B), resta (Z=A-B), transfiere A (Z=A), incrementa A en 1 (Z=A-1).

## Solución

Los apartados A), B) y C) son similares a las cuestiones planteadas en los problemas 4-1, 4-2 y 4-3, en los que se pide obtener la tabla de la verdad, la función lógica y diseñar el circuito AND-OR de diferentes circuitos sumadores y restadores. El apartado D) es análogo al problema 4-30.

A) Obtenga la tabla de la verdad de las salidas  $(c_1, s_1, s_0)$  del sumador de la Fig. 1 en función de las entradas  $(y_1, y_0, x_1, x_0)$ .

| y <sub>i</sub> | <b>y</b> o | $\mathbf{x_1}$ | X <sub>0</sub> | C <sub>1</sub> | $\mathbf{s}_1$ | Sq  |

|----------------|------------|----------------|----------------|----------------|----------------|-----|

| 0              | 0          | 0              | 0              | 0              | 0              | 0   |

| 0              | 0          | 0              | 1              | 0              | 0              | 1   |

| 0              | 0          | 1              | 0              | 0              | 1              | 0   |

| 0              | 0          | 1              | 1              | 0              | 1              | 1   |

| 0              | 1          | 0              | 0              | 0              | 0              | 1   |

| 0              | 1          | 0              | 1              | 0              | 1              | 0   |

| 0              | 1          | 1              | 0              | 0              | l              | . 1 |

| 0              | - 1        | 1              | 1              | 1              | 0              | 0   |

| 1              | 0          | 0              | 0              | 0              | 1              | 0   |

| 1              | 0          | 0              | 1              | 0              | 1              | 1   |

| 1              | 0          | 1              | 0              | 1              | 0              | 0   |

| 1              | 0          | 1              | 1              | 1              | 0              | 1   |

| 1              | 1          | 0              | 0              | 0              | 1              | 1   |

| 1              | 1          | 0              | 1              | 1              | 0              | 0   |

| i              | 1          | 1              | 0              | 1              | 0              | 1   |

| 1              | 1          | -1             | 1              | 1              | 1              | 0   |

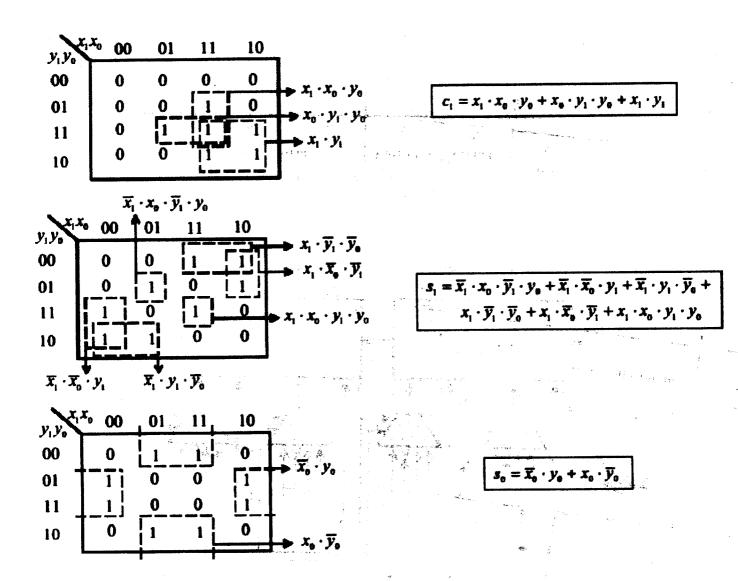

B) Obtenga las funciones lógicas simplificadas de las tres salidas  $(c_1, s_1, s_0)$  del sumador de la Fig. 1 en función de las entradas  $(y_1, y_0, x_1, x_0)$ . Emplee para ello mapas de Karnaugh.

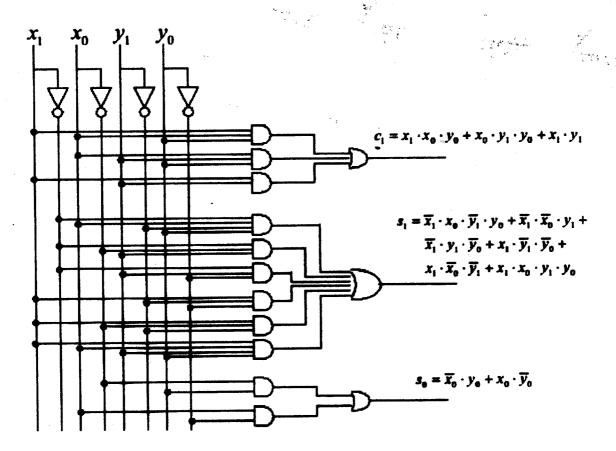

C) A partir de las funciones lógicas calculadas en el apartado anterior, realizar el sumador binario de 2 bits mostrado en la Fig. 1 mediante un circuito combinacional de dos niveles (AND-OR).

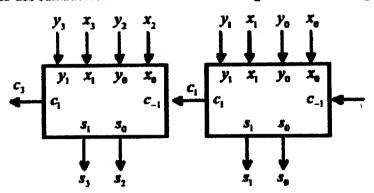

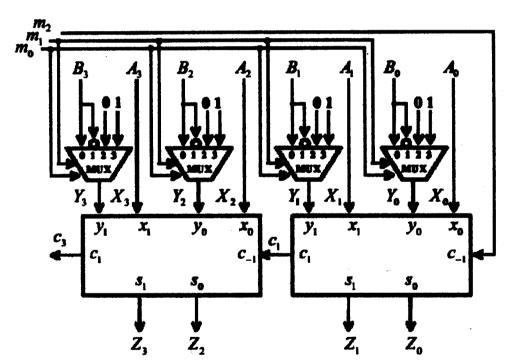

D) Si al sumador binario de la Fig. 1 se le añade una nueva entrada, "bit de arrastre de la etapa anterior" (c.<sub>1</sub>), se obtiene el sumador representado en la Fig. 2. Empleando módulos sumadores como el mostrado en la Fig.2, multiplexores y puertas lógicas, diseñe una ALU aritmética de 4 bits que realice las cinco operaciones siguientes sobre dos números A y B de 4 bits: suma (Z=A+B), resta (Z=A-B), transfiere A (Z=A), incrementa A en 1 (Z=A+1) y decrementa A en 1 (Z=A-1).

En el apartado 4.1.4 del texto de teoría se explica cómo realizar la conexión de circuitos sumadores con bit de acarreo y bit de arrastre de la etapa anterior, con el fin de obtener sumadores de un mayor número de bits. Puede conseguirse un sumador de 4 bits, conectando dos sumadores de 2 bits como el de la Fig. 2, de la forma siguiente:

En el problema 4-30 se explica cómo realizar una ALU, empleando un sumador de 4 bits y multiplexores, que proporciona la funcionalidad pedida en el enunciado del apartado D) del examen. El diseño se realiza de la forma siguiente:

La ALU tiene tres señales de control:  $m_0$ ,  $m_1$  y  $m_2$ . La selección de las entradas de datos de los multiplexores se hace mediante  $m_0$  y  $m_1$ . La entrada  $m_2$  se conecta al arrastre de entrada del primer sumador. Las operaciones aritméticas pedidas en el enunciado pueden generarse de la manera siguiente:

| Schales de control |                |     | Entradas | Selida |           |

|--------------------|----------------|-----|----------|--------|-----------|

| m <sub>2</sub>     | m <sub>1</sub> | M., | x        | Y      | Z         |

| 0                  | 0              | . 0 | Α        | В      | A+B       |

| 1                  | 0              | 1   | A        | Ē      | A+B+1=A-B |

| 0                  | 1              | . 0 | A -      | 0000   | A         |

| 1                  | 1              | 0   | A        | 0000   | A+1       |

| 0                  | 1              | 1   | A        | 1111   | A-1       |

| 1                  | 1<br>1<br>1    | _   | A A      | 0000   |           |