```

3:

B \leftarrow Bus;

4:

for Cont = 0 to 7 do

5:

if Cont es par then

A \leftarrow A + B; A \leftarrow A / 2

6:

7:

else

B \leftarrow B - A; B \leftarrow B * 2

8:

9:

10:

endfor

11:

Bus \leftarrow A;

12:

Bus \leftarrow B;

13:

Parar;

```

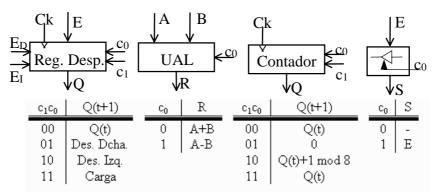

Figura 98-2-1 Módulos del problema con sus tablas de funcionamiento

## **B**ó n

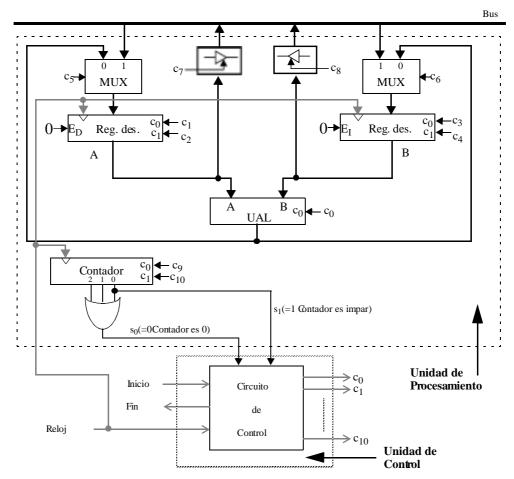

A) En la Figura 98-22 se muestra un posible diseño de la Unidad de Procesamiento y la Tabla 98-21 el significado de todas la señales de control utilizadas. Repasando en algoritmo vemo que permite realizar todos y cada uno de sus pasos:

- Los registros A y Bpueden cargar valores desde el bus del sistema o desde la salida de la UAL.Un multiplexor a à entrada de cada uno de estos registros permite seleccionar qué dato es el que se va a cargar.

- Los registros A y Bpueden volcar sus valores en el bus mediante sendos circuitos triestado de conexión unidireccional con control de 8 bits.

- Existe camino de los registros A y Ba la entrada de la UAL.

- Un contador módulo 8 permite gobernar el bucle for del algoritmo.

- A partir del valordel contador se generan dos condiciones cuyo valor puede ser consultado por la Unidad de Control en cualquie instante:

- •s<sub>o</sub>: es la suma lógica de todos los bits del sumador. Su valor es cero cuando el contador está a cero.

$\bullet$ s<sub>1</sub>: es el bit menos significativo del contador. Suvalor es 0 cuando el contador tiene valor par, y es 1 cuando el contador tiene valor impar.

Figura 98-2-2 Diseño de la Unidad de Proesamiento

| Señal de Control                 | Operacióncontrolada                                                             |

|----------------------------------|---------------------------------------------------------------------------------|

| c <sub>0</sub>                   | Control de la UAL: Suna (0) y Resta (1),                                        |

| c <sub>2</sub> y c <sub>1</sub>  | Control registro A: Nada (00), Des. Dcha.(01), Des. Izq. (10) y Carga (11)      |

| c <sub>4</sub> y c <sub>3</sub>  | Control registro B: Nada (00), Des. Data. (01), Des. Iq. (10) y Carga (11)      |

| c <sub>5</sub>                   | Selección MUX <b>p</b> trada de A: UAL (0)y Bus (1)                             |

| c <sub>6</sub>                   | Selección MUX netrada de B: UAL(0) y Bus (1)                                    |

| c <sub>7</sub>                   | Puerta triestado que conecta la salida de A con el Bus: Nada (0)y Conexión (1)  |

| c <sub>8</sub>                   | Puerta triestado que conecta la salida de B con el Bus: Nada (0) y Conexión (1) |

| c <sub>10</sub> y c <sub>9</sub> | Contador: Nada (00), Reset (01), Incrementar (10) y Nada (11)                   |

Tabla 98-2-1: Descripción de la señales de control de la Unidad de Pocesamiento

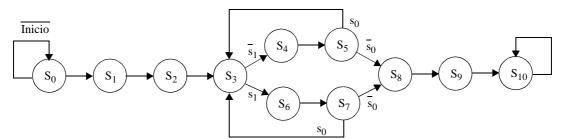

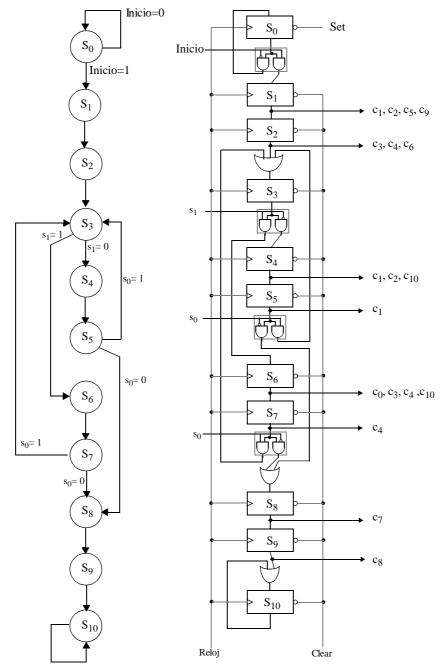

**B**) Para describir el funcionamiento de la Unidad de Control, diseñamos el diagrama de transición de estados de la Figura 98-2-3 donde la descripción detallada de las aciones a realizar en cada un de estos estados viene dad a en la Tabla 98-2-2.

Este diagrama de transición de estados cumple todos los requisitos para ejecutar el algoritmopropuesto en el enunciado del problema utilizando la Unidad de Procesamiento diseñada en el apartado anterior. Se puede comprobar, por ejemplo, que ejecuta el bucle *for* 8 veces.

Figura 98-23: Diagrama de estados de la Unidad de Control

| Estadode la Unidad<br>de Control | Microoperaciones<br>efectuadas | Señales de control<br>a activar                                                          |

|----------------------------------|--------------------------------|------------------------------------------------------------------------------------------|

| $S_0$                            | Ninguna                        | Ninguna                                                                                  |

| S <sub>1</sub>                   | A← Bus<br>Reset Cont           | c <sub>1</sub> , c <sub>2</sub> , c <sub>5</sub> , c <sub>9</sub> , (c <sub>10</sub> =0) |

| $S_2$                            | B ← Bus                        | $c_3, c_4, c_6$                                                                          |

| S <sub>3</sub>                   | Ninguna                        | Ninguna                                                                                  |

| S <sub>4</sub>                   | A ← A+B<br>Incrementar Cont    | $(c_0=0), c_1, c_2, (c_5=0), c_{10}, (c_9=0)$                                            |

| S <sub>5</sub>                   | Desplazar Derecha A            | (c <sub>2</sub> =0), c <sub>1</sub>                                                      |

| S <sub>6</sub>                   | B ← B - A<br>Incrementar Cont  | $c_0, c_3, c_4, (c_6=0), c_{10}, (c_9=0)$                                                |

| S <sub>7</sub>                   | Desplazar Izquierda B          | c <sub>4</sub> , (c <sub>3</sub> =0)                                                     |

| S <sub>8</sub>                   | Bus ← A                        | c <sub>7</sub>                                                                           |

| S <sub>9</sub>                   | Bus ← B                        | c <sub>8</sub>                                                                           |

| S <sub>10</sub>                  | Ninguna                        | Ninguna                                                                                  |

Tabla 98-22: Acciones tomadas por la Unidad de Control en cada estado

Para implementar esta Unidad de Control vamos a empl**a**r el método de los elementos de **e**tardo. El diseño correspondiente se muestra en la Figura 98-2-4.

Figura 98-2-4 Unidad de Control