#### Tema 3

Tema 3: Lógica Combinacional (II): Ruta de Datos.

#### TEMA 3: LÓGICA COMBINACIONAL (II): RUTA DE DATOS

- Contexto

- Conocimiento Previo Necesario

- Objetivos del Tema

- Guía de Estudio

- Contenido del Tema

- 3.1. Circuitos Selectores de Datos (Multiplexos)

- 3.2. Demultiplexos

- 3.3. Codificadores con Prioridad

- 3.4. Amplificadores (buffers-drivers) y Transmisores-receptores de Bus

- 3.5. Problemas

- Preparación de la Evaluación

#### +++ OBJETIVOS DEL TEMA

- **Objetivo 1:** Comprender la estructura interna y la función de los multiplexos en su doble uso como:

- a) Selector de canales de entrada (1 de n, paso de información de paralelo a serie)

- b) Módulo de diseño de otros circuitos en lógica combinacional.

- **Objetivo 2:** Comprender los demultiplexos y su uso como:

- a) Selector de canales de salida (1 de n, paso de información de serie a paralelo)

- b) Módulo de diseño (junto con los Multiplexos) de circuitos convertidores de código.

- Objetivo 3: Conocer los circuitos encargados de adaptar las señales en su interacción con un "bus": amplificadores (buffers-drivers) y transmisores-receptores de bus (bustransceivers).

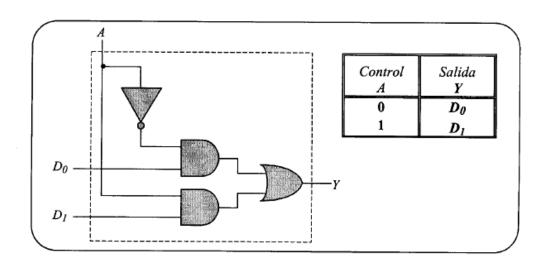

# 6.1 Circuitos selectores de datos (Multiplexor)

Multiplexor = circuito con "N" entradas, 1 salida y "n" patillas de selección, tal que 2<sup>n</sup>=N. Con la combinación binaria introducida en las patillas de selección (n), elegimos la entrada N que aparecerá en la salida.

Figura 6.1. Circuito multiplexor de 2 a 1.

### м

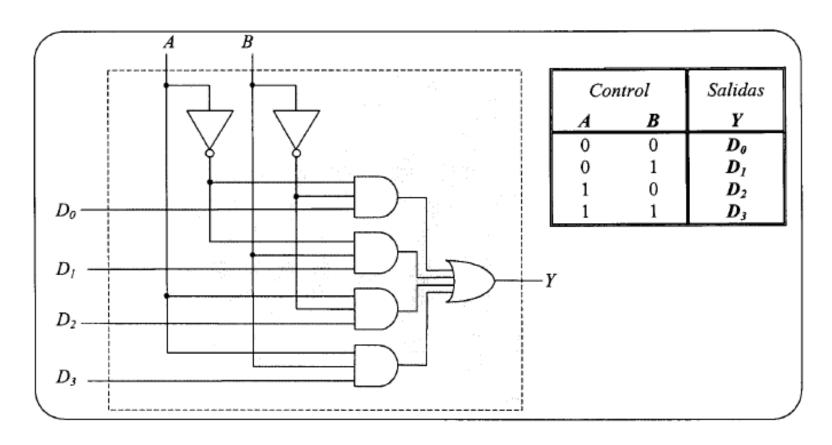

### Multiplexor de 4 canales

Figura 6.2. Circuitos multiplexores de 4 a 1.

# .

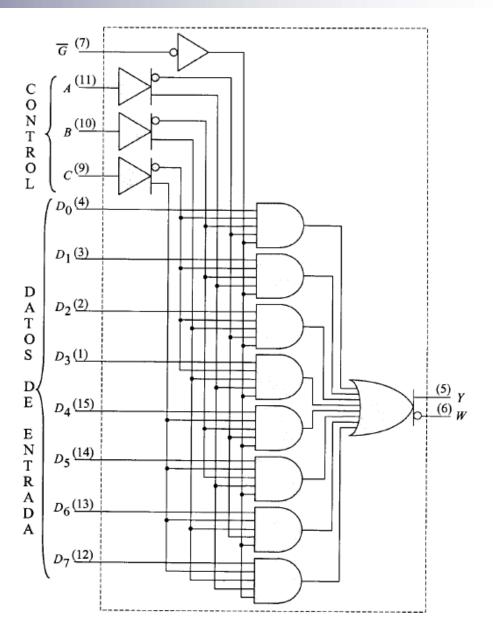

### Multiplexor de 8 canales

Figura 6.3. Circuito interno del Multiplexo AS151.

(a)

|     | ENT       | SALI  | IDAS      |                       |                         |

|-----|-----------|-------|-----------|-----------------------|-------------------------|

| Con | trol de C | Canal | Strobe    | JAL                   | DAS                     |

| С   | В         | A     | $\bar{G}$ | Y                     | W                       |

| х   | х         | х     | Н         | L                     | H                       |

| L   | L         | L     | L         | $D_{\theta}$          | $\overline{D}_{\theta}$ |

| L   | L         | Н     | L         | $D_1$                 | $\overline{D}_{1}$      |

| Ļ   | Н         | L     | L         | $D_2$                 | $\overline{D}_2$        |

| L   | Н         | Н     | L         | $D_3$                 | $\overline{D}_3$        |

| Н   | L         | L     | L         | $D_4$                 | $\overline{D}_4$        |

| Н   | L         | H     | L         | D 5                   | $\overline{D}_5$        |

| Н   | Н         | L     | L         | $D_6$                 | $\overline{D}_6$        |

| Н   | Н         | Н     | L         | <b>D</b> <sub>7</sub> | $\overline{D}_7$        |

| $ \begin{array}{c cccc} C & (9) & & & & & & \\ D_0 & (4) & & & & & & \\ D_1 & (3) & & & & & \\ D_1 & (3) & & & & & \\ D_2 & (2) & & & & & \\ D_3 & (1) & & & & & \\ D_3 & (15) & & & & & \\ D_4 & (15) & & & & & \\ D_5 & (14) & & & & & \\ D_6 & (13) & & & & & \\ D_7 & (12) & & & & & \\ \end{array} $ (5)  (6)  (7) | Y |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $D_7^{(12)}$ 7                                                                                                                                                                                                                                                                                                          |   |

Figura 6.4. (a) Tabla de verdad del Multiplexo AS151. (b) Símbolo lógico.

**(b)**

#### Síntesis de una función

- Las variables de control (A, B) representan a dos variables cualesquiera de la función a sintetizar.

- 2. Los canales de datos (D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>) se usan para la tercera variable (Z). El rango de valores para los D<sub>i</sub> es (0,1,Z,Z). Si un determinado producto X·Y no existe, ponemos la D<sub>i</sub> correspondiente a "0". Si existe y no tiene Z, ponemos su D<sub>i</sub> a "1". Si tiene Z, ponemos el valor correspondiente (Z ó Z).

| $m_0 = 0 \ 0 \ \overline{X} \overline{Y}$ 1 $D_0 = 1$ MUX                                                                        | A B | XY              | Residuo | Valor de D <sub>i</sub> | 1"——<br>] | $\bigcup_{D_1}^{D_0}$ |       |

|----------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|---------|-------------------------|-----------|-----------------------|-------|

| $ \begin{vmatrix} m_2 = 1 & 0 & X \overline{Y} \\ m_3 = 1 & 1 & X \overline{Y} \end{vmatrix}                                   $ | 1   | l —             | 1<br>Z  |                         |           | MUX                   | f(XY) |

| $m_3 = 1 \ 1  X \ Y \qquad Z \qquad D_3 = Z \qquad Z$                                                                            | i   | $X\overline{Y}$ |         | _                       |           |                       |       |

| (a) (b) X Y                                                                                                                      |     | XY              | Z       | $D_3 = Z$               |           |                       |       |

Do

Figura 6.5. Diseño de funciones lógicas usando multiplexos. Ilustración del ejemplo usando un multiplexo de cuatro entradas (D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub> y D<sub>3</sub>) y dos líneas de control (A y B). (a) Tablas de la función a sintetizar y los valores de D<sub>i</sub> para la variable residual. (b) Esquema de conexión del circuito.

## м

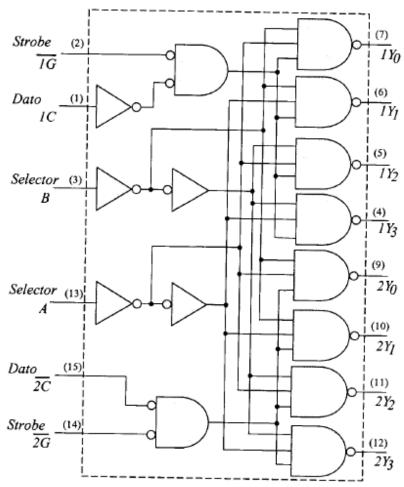

#### 6.2 Demultiplexos

Circuito con "1" entradas, N salida y "n" patillas de selección, tal que 2<sup>n</sup>=N. Con la combinación binaria introducida en las patillas de selección (n), elegimos là salida N en la que aparecerá la entrada.

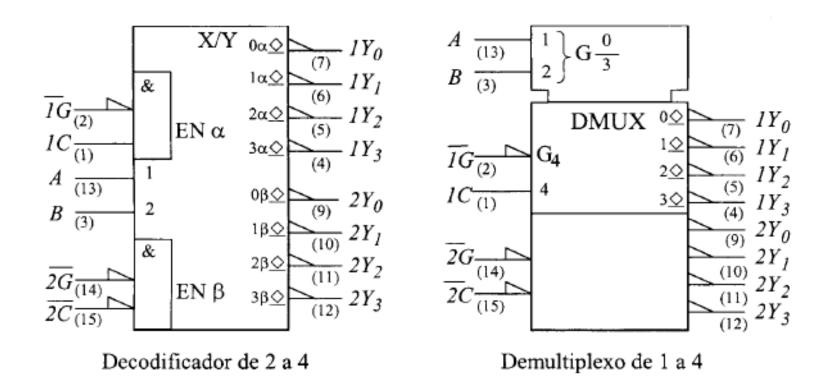

Figura 6.7. Circuito interno del SN74ALS156 que incluye dos demultiplexos 1 a 4 con direccionamiento común (A,B) y entrada de facilitación/inhibición individual  $(I\overline{G} y 2\overline{G})$ .

Figura 6.8. Símbolos lógicos del circuito ALS156. (a) Decodificador de 2 a 4. (b) DEMUX dual de 1 a 4.

| ENT   | RAD! | AS              | SALIDAS         |               |        |     |     |

|-------|------|-----------------|-----------------|---------------|--------|-----|-----|

| Selec | ción | Strobe          | Dato            |               | SALI   | DAS |     |

| В     | A    | $2\overline{G}$ | $2\overline{C}$ | $2Y_{\theta}$ | $2Y_I$ | 2Y2 | 2Y3 |

| х     | х    | Н               | х               | Н             | Н      | Н   | Н   |

| L     | L    | L               | L               | L             | Н      | Н   | Н   |

| L     | Н    | L               | L               | Н             | L      | Н   | Н   |

| Н     | L    | L               | L               | Н             | Н      | L   | Н   |

| Н     | Н    | L               | Ĺ               | Н             | Н      | Н   | L   |

| Х     | Х    | X               | Н               | Н             | Н      | Н   | Н   |

Figura 6.9. Circuito ALS156. Tablas de verdad para controlar el funcionamiento del circuito como decodificador de 2 a 4 y como DEMUX doble de 1 a 4.

Así pues, los circuitos demultiplexores/decodificadores intervienen en el diseño lógico a tres niveles:

- a) Funciones específicas de distribución de datos.

- Funciones específicas de decodificación.

- c) Como módulos generales de diseño.

| DESCRIPCIÓN                                             | TIPO de SALIDA   | NOMBRE<br>(SN74xxx) |

|---------------------------------------------------------|------------------|---------------------|

| DEMUX de 4 a 16                                         | Tres estados     | 154                 |

| 4 a 16                                                  | Colector abierto | 159                 |

| 4 a 10 (BCD a Decimal)                                  | Dos estados      | 42                  |

| 4 a 10 (Exceso 3 a Decimal)                             | Dos estados      | 43                  |

| 3 a 8 con biestables en las tres<br>líneas de dirección | Dos estados      | 137                 |

| Dual 2 a 4                                              | Dos estados      | 139                 |

| BCD a Decimal                                           | Colector abierto | 141                 |

| BCD a Siete Segmentos                                   | " "              | 246                 |

Figura 6.10. Algunos ejemplos de circuitos demultiplexos y decodificadores específicos.

### ٧

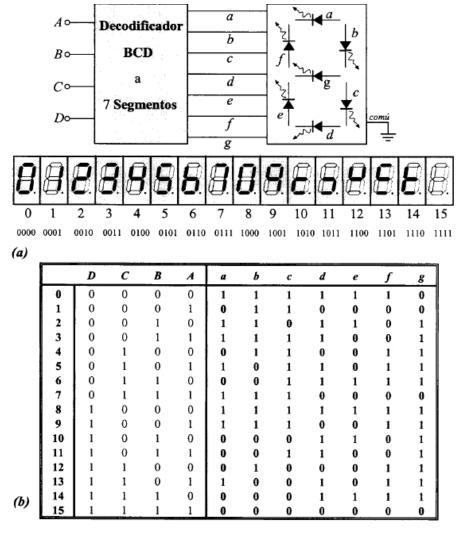

#### Uso como decodificador BCD a decimal

El uso es muy sencillo, ya que, se pondrá la entrada a un nivel lógico fijo (1 o 0 según interese) y luego mediante la combinación binaria que metamos en las patillas de selección conseguiremos el nivel lógico introducido a la entrada en la salida seleccionada, conformando con ello un decodificador.

|   | CÓDIG | O BCD |   |                                                                |

|---|-------|-------|---|----------------------------------------------------------------|

| 8 | 4     | 2     | 1 | DECIMAL                                                        |

| D | С     | В     | A | {D <sub>i</sub> }                                              |

| 0 | 0     | 0     | 0 | $D_0 = \overline{D}  \overline{C}  \overline{B}  \overline{A}$ |

| 0 | 0     | 0     | 1 | $D_1 = \overline{D}  \overline{C}  \overline{B}  A$            |

| 0 | 0     | 1     | 0 | $D_2 = \overline{D}  \overline{C}  B  \overline{A}$            |

| 0 | 0     | 1     | 1 | $D_3 = \overline{D}  \overline{C}  B  A$                       |

| 0 | 1     | 0     | 0 | $D_4 = \overline{D} C \overline{B} \overline{A}$               |

| 0 | 1     | 0     | 1 | $D_5 = \overline{D} C \overline{B} A$                          |

| 0 | 1     | 1     | 0 | $D_6 = \overline{D} C B \overline{A}$                          |

| 0 | 1     | 1     | 1 | $D_7 = \overline{D} C B A$                                     |

| 1 | 0     | 0     | 0 | $D_8 = D \overline{C} \overline{B} \overline{A}$               |

| 1 | 0     | 0     | 1 | $D_9 = D  \overline{C}  \overline{B}  A$                       |

Figura 6.11. Decodificador BCD a decimal. Tabla de verdad y funciones lógicas asociadas a cada dígito decimal.

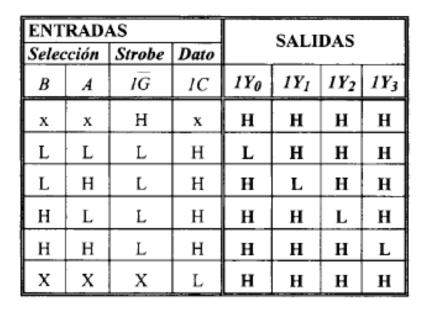

Figura 6.12. Síntesis del decodificador BCD a decimal.

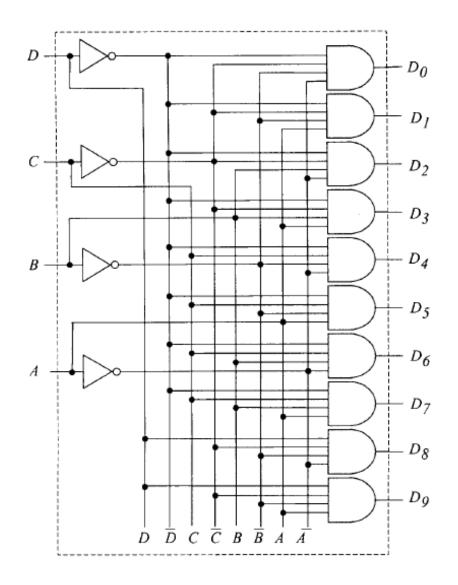

#### Decodificador BCD a 7 segmentos

Figura 6.13. Decodificador BCD a 7 segmentos. (a) Código de diodos usado para representar los dígitos. (b) Tablas de verdad.

### M

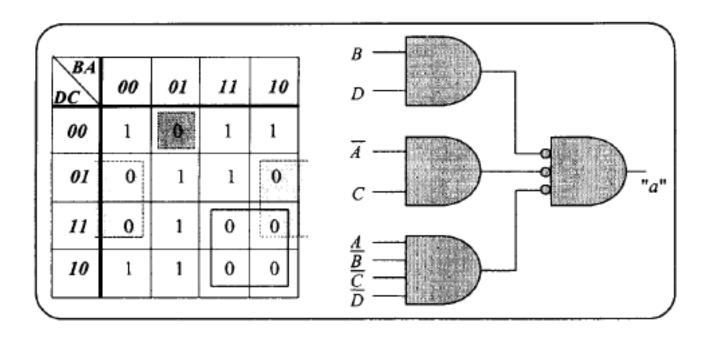

### Síntesis del segmento a

Figura 6.14. Síntesis del segmento "a".

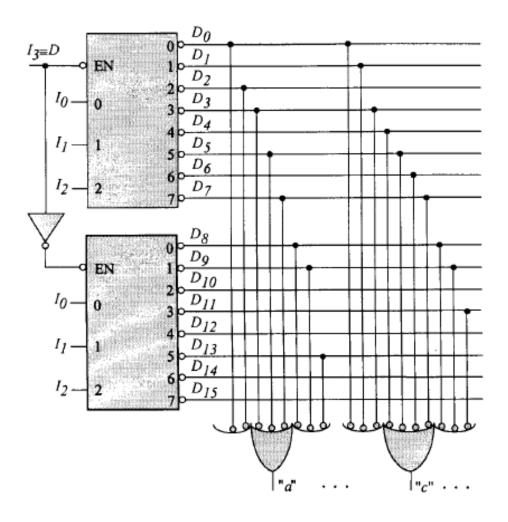

Figura 6.15. Uso de circuitos demultiplexores en la síntesis de funciones lógicas. Ejemplo de uso de dos circuitos 3 a 8 conectados a través del terminal de facilitación/inhibición para producir 16 términos mínimos. Las puertas OR con las conexiones indicadas sintetizan los segmentos "a" y "c" del decodificador del ejemplo anterior.

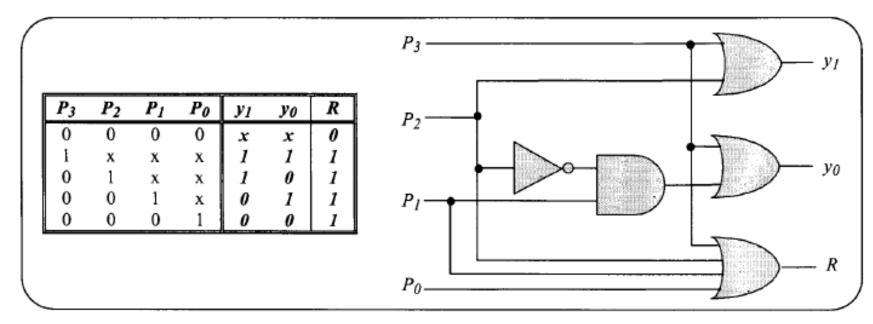

#### 6.3 Codificadores con prioridad

- Un circuito codificador genera una salida en función del código correspondiente a la entrada activa.

- Si están activadas más de una entrada es necesario establecer un criterio de prioridad de forma que en todo momento sólo se genere el código de la línea más prioritaria de entre todas las activas.

- A este tipo de codificadores se les denomina codificadores con prioridad

Figura 6.16. Tabla de verdad y circuito correspondiente al diseño de un codificador con cuatro niveles de prioridad. Se considera que P<sub>3</sub>, P<sub>2</sub>, P<sub>1</sub>, P<sub>0</sub> y R son activas en baja y que y<sub>1</sub> e y<sub>0</sub> son activas en alta.

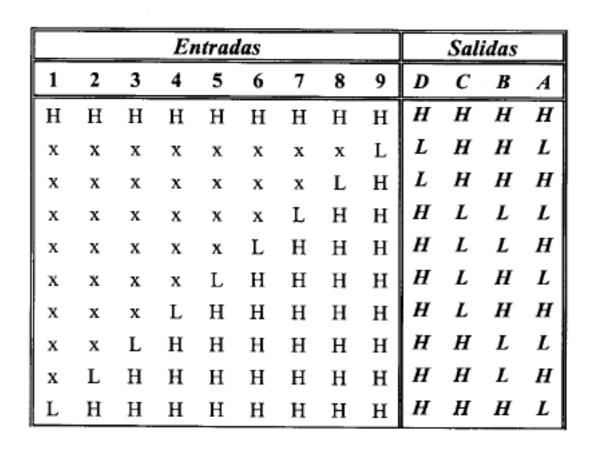

Figura 6.17. Tabla de verdad correspondiente al codificador con prioridad SN74147.

# M

#### 6.4 Amplificadores (Buffers-Drivers) y Transmisores-Receptores de Bus

Circuitos integrados que sirven para amplificar la corriente de las señales y para configurar los buses de comunicación de los sistemas microprocesadores

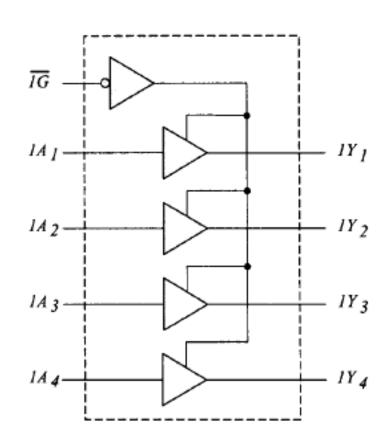

Figura 6.19. Circuitos amplificadores ("Buffers-Drivers") tipo ALS760 (medio circuito).

| CONTROL        |     | OPERACIÓN            |

|----------------|-----|----------------------|

| $\overline{G}$ | DIR |                      |

| 0              | 0   | Datos de B pasan a A |

| 0              | 1   | Datos de A pasan a B |

| 1              | Х   | Aislamiento          |

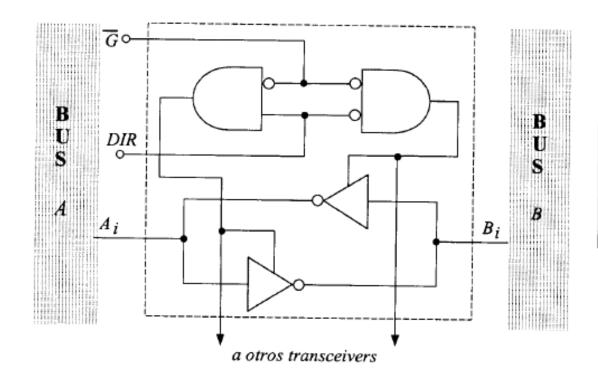

Figura 6.20. Transmisor-receptor de canal (ALS641).

| R₃ | $R_2$ | $R_I$ | $R_{\theta}$ | $E_3$ | $E_2$ | $E_1$ | $E_0$ | R₃ ≎—   |  |

|----|-------|-------|--------------|-------|-------|-------|-------|---------|--|

| 1  | х     | х     | х            | 1     | 0     | 0     | 0     |         |  |

| 0  | 1     | x     | х            | 0     | 1     | 0     | 0     | R₂      |  |

| 0  | 0     | 1     | x            | 0     | 0     | 1     | 0     |         |  |

| 0  | 0     | 0     | 1            | 0     | 0     | 0     | 1     |         |  |

| 0  | 0     | 0     | 0            | 0     | 0     | 0     | 0     | $R_1$ ° |  |

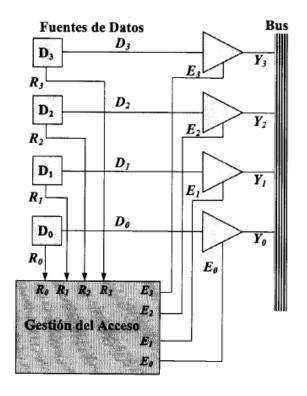

Figura 6.21. Gestión del acceso a un bus de cuatro fuentes de datos..

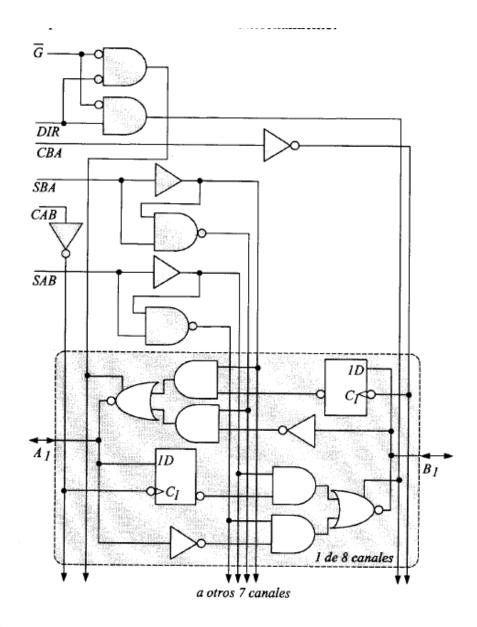

Figura 6.22. Circuito interno del octal bus transceiver ALS646