imagination sense

# TEORÍA

## DE ELECTROPICA DIGITAL

A. E. Delgado

J. Mira

S. Dormido Canto

SANZ Y TORRES S.L.

### TEORÌA DE ELECTRÒNICA DIGITAL

A. E. DELGADO J. MIRA S. DORMIDO CANTO

#### Prólogo a la segunda edición

En esta segunda edición del libro hemos procurado corregir los errores y erratas detectados en la edición anterior e introducir explicaciones más detalladas en aquellos problemas en los que nuestros alumnos habían detectado excesiva parquedad en el procedimiento de solución.

Es decir, hemos hecho más énfasis en los aspectos tutoriales, básicos en la enseñanza a distancia.

#### **CONTENIDO**

| 1             | Exigencias Computacionales Del Procesamiento Digital De La Información   |

|---------------|--------------------------------------------------------------------------|

| 2             | Dispositivos Semiconductores En Corte Y Saturación                       |

| 3             | Familias Lógicas (I): TTL                                                |

| 4             | Familias Lógicas (II) : ECL, MOS, CMOS Y BiCMOS                          |

| 5             | Lógica Combinacional (I): Funciones Aritmético – Lógicas                 |

| 6             | Lógica Combinacional (II) : Ruta De Datos                                |

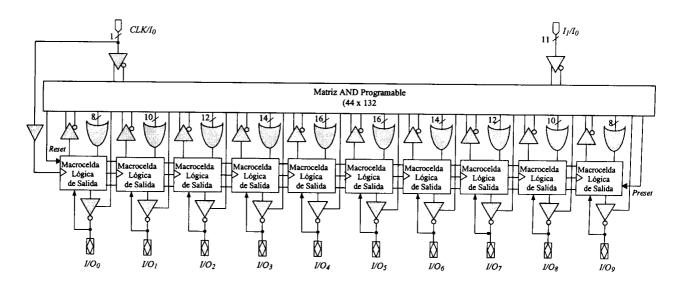

| 7             | Lógica Combinacional Programable                                         |

| 8             | Exigencias Computacionales De La Lógica Secuencial: Circuitos Biestables |

| 9             | Introducción Al Diseño Secuencial: Contadores Y Registros                |

| 10            | Temporizadores Y Relojes                                                 |

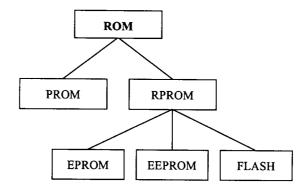

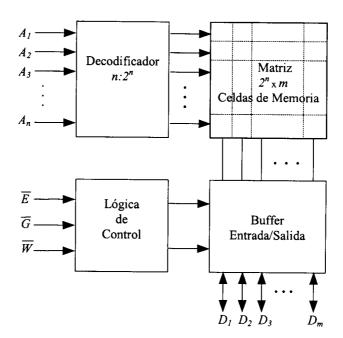

| 11            | Memorias RAM Y CAM                                                       |

| 12            | Memorias De Acceso Secuencial                                            |

| 13            | Lógica Secuencial Programable: CPLDs Y FPGAs                             |

| Apéndice<br>A | Resumen De Física De Semiconductores                                     |

| Apéndice<br>B | Símbolos Lógicos                                                         |

### Exigencias Computacionales del Procesamiento Digital de la Información

#### + CONTEXTO

El propósito general de este tema es describir el modelo matemático que subyace a los circuitos combinacionales. Es decir, la representación digital (binaria) de la información y los operadores básicos del álgebra de Boole. Después estudiamos las distintas formas de representar funciones lógicas, los cambios de representación y la minimización.

Estas funciones lógicas serán usadas posteriormente para describir el comportamiento externo de todos los circuitos combinacionales, llamados así porque en el caso ideal su respuesta en un instante sólo depende del valor de las entradas en ese mismo instante. Estos circuitos están relacionados con todos aquellos aspectos de la computación encargados de controlar la ruta de

datos y de realizar operaciones aritméticas o lógicas con esos datos.

Este tema es el primero del texto y su contenido es básico para todos los demás. Sus antecedentes son de naturaleza lógica y los estudia el alumno, en general, de forma concurrente.

#### ++ CONOCIMIENTO PREVIO NECESARIO

El nivel de descripción del tema es muy elemental por lo que no se necesitan conocimientos previos específicos. Vamos a introducir la distinción entre procesado analógico y digital y después iremos introduciendo y explicando todos los conceptos a medida que sean necesarios para el desarrollo del tema. Conviene recordar aquí la equivalencia del álgebra de Boole con los temas análogos que, posiblemente, haya estudiado el lector en los textos de Lógica.

#### +++ OBJETIVOS DEL TEMA

Los objetivos del tema deben coincidir con lo que queremos que el alumno sepa al final del tema y esto se puede especificar en extenso, dando la descripción general de cada uno de los objetivos. Tras el estudio de este tema el alumno deberá haber alcanzado los siguientes objetivos:

- **Objetivo 1:** Distinguir claramente entre el procesado analógico y digital, entendiendo que son dos formas diferentes de representar la información (los datos) y de operar con ellos para obtener otros datos.

- **Objetivo 2:** Conocer los postulados y teoremas básicos del Álgebra de Boole y saber demostrar los teoremas.

- Objetivo 3: Saber representar funciones lógicas usando distintos tipos de operadores (AND, OR, NOT; sólo NAND; sólo NOR) y saber pasar de una representación a otra. Por ejemplo, de (AND, OR, NOT) a sólo NAND o de NAND a NOR o de términos mínimos (suma de productos) a términos máximos (productos de sumas).

- **Objetivo 4:** Saber analizar un circuito lógico. Es decir, saber pasar del esquema de un circuito a la expresión o expresiones lógicas que enlazan las variables de entrada al circuito con las variables de salida.

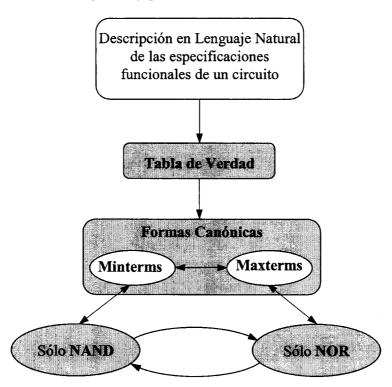

- Objetivo 5: Saber sintetizar un circuito lógico. Es decir: (a) saber pasar de un conjunto de especificaciones funcionales a una tabla de verdad, (b) de una tabla de verdad a una o más funciones lógicas y (c) de estas funciones al circuito que las satisface.

- Objetivo 6: Saber minimizar funciones lógicas. Es decir, dada una cierta función lógica, encontrar otra equivalente (con la misma tabla de verdad) pero con menos términos o con términos con menos variables. Este objetivo está enlazado con el objetivo 2, porque el proceso de minimización se basa en el uso adecuado y repetido de los postulados y teoremas del Álgebra de Boole. Sin embargo, para alcanzarlo es conveniente usar el conocimiento adicional del método de Karnaugh que recoloca los distintos términos de forma tal que hace evidente el proceso de minimización para funciones de hasta 4 ó 5 variables.

#### ++++ GUÍA DE ESTUDIO

Al ser el primer tema, las recomendaciones referentes al contenido son las de identificar en cada momento en qué objetivo nos encontramos y usar ejemplos para comprobar nuestras propuestas de minimización, análisis y síntesis. Siempre usamos ejemplos con pocas variables porque así es relativamente sencillo comprobar las funciones que calculan los distintos circuitos, los postulados, los teoremas y los resultados de una minimización usando las tablas de verdad y/o los diagramas de Venn. Es decir, comprobando para todas y cada una de las configuraciones de entrada, cuál es la configuración de salida (inducción completa).

#### Contenido del Tema

#### 1.1. PROCESAMIENTO DIGITAL DE LA INFORMACIÓN

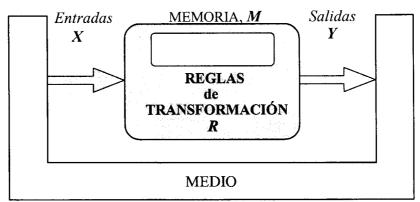

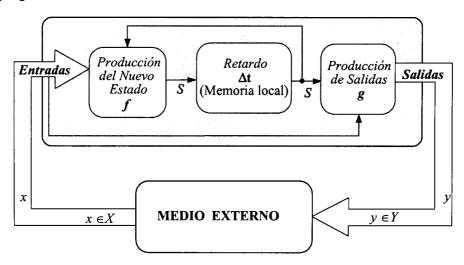

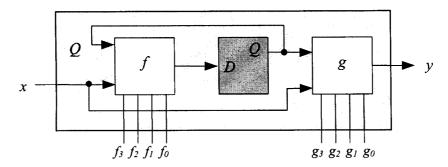

Todo sistema que procesa información puede ser descrito de acuerdo con el modelo computacional de la figura 1.1. Se comienza distinguiendo entre medio y sistema y el comportamiento del sistema se describe en términos de un conjunto de variables de entrada,  $X = \{x_i(t)\}$ , un conjunto de variables de salida,  $Y = \{y_j(t)\}$ , y un conjunto de reglas de transformación,  $R = \{r_{ij}^k(t)\}$ , que realizan procesos sobre las variables de entrada y los contenidos de memoria,  $M = \{m_k(t)\}$ , para generar los valores de las variables de salida y modificar los contenidos de memoria. Toda computación puede describirse entonces en términos de un conjunto de señales, (X, Y, M), que representan la información y de un conjunto de reglas, R, que especifican los procesos que se usan para transformar la representación de entrada, X, en la correspondiente representación de salida, Y.

Las variables de *entrada* y salida son magnitudes físicas, en general señales eléctricas (tensiones o corrientes), que sirven de soporte material de la información que se va a procesar. Estas señales pueden ser analógicas o digitales. Una señal analógica,  $x_A(t)$ , admite valores de un espectro continuo entre ciertos valores extremos que marcan su rango dinámico. Por ejemplo, puede ser una señal periódica de tipo sinusoidal que varía entre +5voltios y -5voltios,  $x_A^I(t) = 5\cos\omega t$ , o una señal en forma de rampa,  $x_A^2(t) = 2t$ .

Por el contrario, una señal digital,  $x_D(t)$ , sólo tiene dos valores posibles, "alto" o "bajo", asociados a dos estados lógicos  $x_D="1"$ ,  $x_D="0"$ . Cualquier magnitud analógica admite una representación digital equivalente y viceversa. Es importante señalar que el valor físico real de los dos estados lógicos no es relevante a nivel conceptual. Por ejemplo, el "1" lógico puede estar asociado a  $x_D=5$  V y el "0" lógico a  $x_D=-5$  V. O bien, el "1" a  $x_D=1$  V y el "0" a  $x_D=0$  V. Veremos más adelante

cómo la selección de unos u otros valores está asociada a ciertos criterios de naturaleza electrónica, tales como la velocidad de conmutación, el tipo de transistor usado en la síntesis de los operadores lógicos (bipolar o MOS), la familia lógica (TTL o ECL, por ejemplo) o la inmunidad al ruido.

Figura 1.1. Modelo computacional básico.

De la misma forma en que la información puede representarse mediante señales analógicas (continuas) o digitales (binarias), las reglas computacionales,  $\{R_A, R_D\}$ , también pueden ser analógicas o digitales. Una regla de computación analógica,  $R_A$ , produce señales de salida, y(t), continuas combinando las entradas y los contenidos de memoria mediante operaciones analógicas lineales o no lineales. Por ejemplo, sumando, multiplicando por una constante, derivando, integrando, etc...). Así, las siguientes expresiones son ejemplos de computación analógica:

$$R_A^I: y(t) = A \cdot x(t)$$

$$R_A^2: y(t) = A_1 \cdot x_1(t) + A_2 \cdot x_2(t)$$

$$R_A^3: y(t) = A_1 \cdot x_1(t) + B \int x_2(t) \cdot dt + C \frac{dx_3(t)}{dt}$$

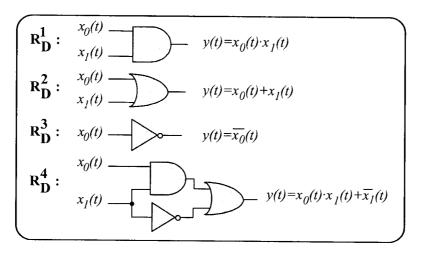

De forma equivalente, una regla de computación digital,  $R_D$ , produce representaciones binarias de salida (vectores lógicos de "ceros" y "unos"), combinando la representación binaria de entrada,  $X_D(t)$ , con el contenido de memoria,  $M_D(t)$ , mediante operadores digitales. Un conjunto completo de estos operadores lo forman la suma lógica (operador "OR"), el producto lógico (operador "AND") y la

inversión o complemento de una variable (operador NOT). Así, las siguientes expresiones (figura 1.2) son ejemplos de computación digital, que se muestran asociadas al símbolo que las representa.

Figura 1.2. Expresiones de computación digital.

Como las magnitudes binarias sólo pueden poseer uno de dos valores, (0,1), los operadores digitales se pueden representar mediante "tablas de verdad" que especifican de forma completa, en extenso, el valor que toma la salida para cada una de las posibles configuraciones de valores en la entrada. Así, para dos variables,  $x_0(t)$ ,  $x_1(t)$ , hay cuatro posibilidades de composición:  $(x_0=0, x_1=0)$ ,  $(x_0=1, x_1=0)$ ,  $(x_0=0, x_1=1)$  y  $(x_0=1, x_1=1)$ , con lo cual la especificación de las reglas usadas como ejemplo es la que se muestra en la figura 1.3.

| $x_{I}$ | $x_0$ | $\overline{x_l}$ | $x_1 \cdot x_0$ | $x_1 + x_0$ | $x_1 \cdot x_0 + \overline{x_1}$ |

|---------|-------|------------------|-----------------|-------------|----------------------------------|

| 0       | 0     | 1                | 0               | 0           | 1                                |

| 0       | 1     | 1                | 0               | 1           | 1                                |

| 1       | 0     | 0                | 0               | 1           | 0                                |

| 1       | 1     | 0                | 1               | 1           | 1                                |

Figura 1.3. Tablas de verdad que especifican en extenso los operadores lógicos usados en el ejemplo a partir de las cuatro configuraciones de valores posibles en las dos variables de entrada,  $(x_0, x_1)$ .

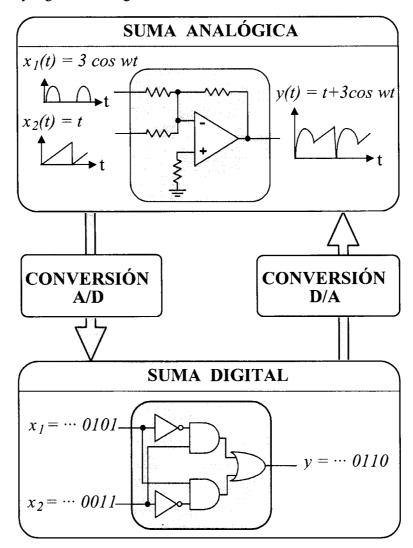

La figura 1.4 ilustra la representación y el procesado digital de la información comparando con

la solución analógica equivalente para el caso de una sencilla suma. Se incluye también las transformaciones que serían necesarias para cambiar de representación, es decir, las conversiones analógicas-digitales y digitales-analógicas.

Figura 1.4. Ilustración cualitativa de la suma analógica comparada con la suma digital

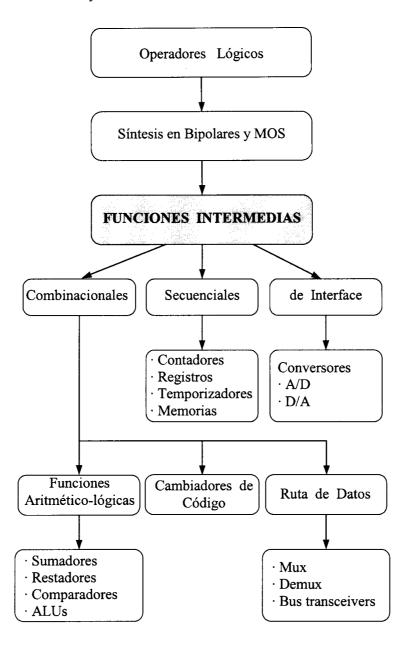

En este texto nos vamos a preocupar de hacer un análisis del conjunto mínimo de operadores digitales necesarios para la síntesis de cualquier procesador digital y de estudiar después su síntesis modular a nivel lógico para incluir finalmente la realización física de esos módulos básicos en las

tecnologías bipolar, MOS y C-MOS. Afortunadamente, el diseño digital y por consiguiente la electrónica que lo soporta son *modulares*, de forma que un conjunto completo de operadores lógicos sólo necesita tres circuitos: AND, OR y NOT. Veremos más adelante que basta una combinación de dos de estos tres operadores (NAND ó NOR) para poder sintetizar cualquier función lógica.

#### 1.2. FUNCIONES COMBINACIONALES Y SECUENCIALES NECESARIAS.

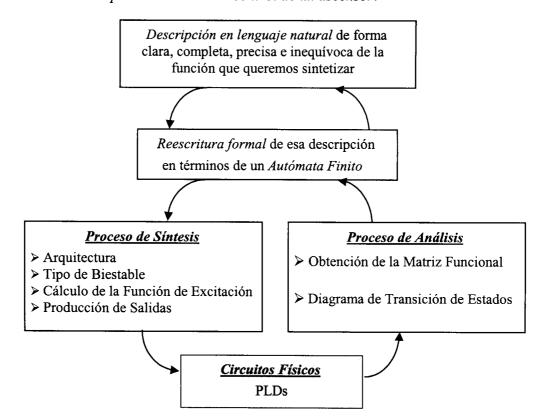

La electrónica digital es una ingeniería. Es decir, su tarea fundamental es la síntesis de circuitos que satisfacen determinadas especificaciones funcionales. Primero aparece una necesidad de procesamiento digital de la información y después buscamos un circuito que satisface esa necesidad siguiendo, aproximadamente, los siguientes pasos:

- 1. Descripción de la computación en lenguaje natural de forma clara, completa, precisa e inequívoca.

- **2.** Traslación de esa descripción a un conjunto de especificaciones funcionales en un lenguaje lógico formal.

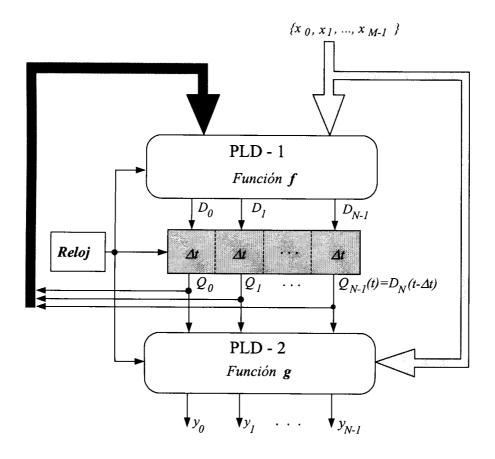

- 3. Reescritura de esa descripción formal en términos del modelo computacional de la figura 1.1. Es decir, en términos de entradas, estados de memoria, salidas y reglas de transformación,  $\{R_D\}$ , que representan la dinámica interna de la computación especificando cómo se producen el nuevo estado y las salidas a partir de las entradas y del estado anterior.

- **4.** Síntesis modular del sistema en términos de un conjunto completo de operadores mínimos.

Todas las funciones necesarias para el procesamiento digital de la información, es decir todas las reglas  $R_D$ , pueden incluirse en dos grandes apartados:

- a) Funciones Combinacionales.

- b) Funciones Secuenciales.

Son funciones de *lógica combinacional* todas aquellas funciones en las que para obtener el valor de la salida en un cierto instante sólo necesitamos conocer el valor de las entradas en ese mismo

instante. Son funciones de decisión, sin "memoria". El modelo matemático soporte de esta parte de la electrónica digital es el *Álgebra de Boole*, de la que más adelante incluiremos un resumen. Ejemplos de este tipo de funciones son entre otras:

- a.1. Operaciones aritmético-lógicas.

- **a.2.** Funciones de ruta de datos: multiplexos y demultiplexos.

- a.3. Circuitos cambiadores de código.

Es cierto que, aunque en el caso ideal las funciones combinacionales son "instantáneas", a la hora de sintetizar físicamente estas funciones usando circuitos integrados reales aparecen pequeños retardos no deseados. El objetivo del diseño en electrónica digital combinacional es hacer mínimo ese retardo que limita la velocidad de conmutación.

Aparece así el primer conjunto de necesidades computacionales. Necesitamos saber representar, analizar y sintetizar circuitos lógicos combinacionales. Es importante que el alumno distinga bien estas tres tareas.

¿Qué es representar?. Representar una función lógica combinacional es encontrar un procedimiento para describir de forma completa la función. Sea cual fuere la configuración de valores en las variables de entrada, la representación debe permitir conocer el valor de la salida. Hay esencialmente dos formas de representación: en extenso y en intenso.

Decimos que una función combinacional está representada *en extenso* cuando poseemos una tabla con todos los valores de las entradas y un vector lógico de salida que nos dice para cada configuración (00··0, 00··1, ..., 11··1), si la salida debe estar en alta (1) ó en baja (0). Las dos formas más usuales de representar funciones lógicas en extenso son las *tablas de verdad* y los *diagramas de Venn*, en los que a cada variable lógica se le asocia un área dentro de un rectángulo.

Decimos que tenemos una función combinacional representada en *intenso* cuando hay una expresión booleana que la describe. Por ejemplo,  $f(x,y,z) = (x\overline{y} + xy)\overline{z}$ . Lógicamente, al dar valores a las variables (x, y, z) obtenemos la tabla en extenso.

¿Qué es analizar?. Analizar un circuito en lógica combinacional es encontrar la representación de las funciones lógicas que lo describen. En el sencillo ejemplo de suma digital mostrado en la figura 1.4 el proceso de análisis debe darnos la expresión lógica de la relación entre las variables

de entrada,  $(x_1,x_2)$  y la salida, y. Siguiendo el camino de las señales es fácil ver que en este caso la función  $y = f(x_1,x_2)$  es de la forma:

$$y = f(x_1, x_2) = (x_1 \bar{x}_2 + \bar{x}_1 x_2)$$

[1.1]

¿Qué es sintetizar?. Es el proceso inverso al de análisis. Partimos ahora de una función lógica,  $y=f(x_1,x_2)$ , ó de un conjunto de N funciones lógicas de M variables,  $y_k(t)=f_k[x_1(t),x_2(t),...,x_M(t)]$ , k=1, 2, ..., N, y buscamos el circuito que realiza físicamente a esa función de forma que reproduce la misma relación entre las variables de entrada y las de salida para todas y cada una de las combinaciones de valores posibles.

El problema de síntesis en sistemas digitales es más complicado que el de análisis porque el punto de partida de la síntesis de un determinado circuito lógico no está especificado con la claridad y precisión de la lógica sino que parte de una descripción en lenguaje natural. Por ejemplo:

Diseñar un circuito que dé paso a la orden de arranque de un coche sólo cuando las puertas  $(x_1)$  estén cerradas  $(x_1=1)$ , el cinturón de seguridad  $(x_2)$  abrochado  $(x_2=1)$ , las luces  $(x_3)$  apagadas  $(x_3=1)$  y el motor  $(x_4)$  no esté ya en marcha  $(x_4=0)$ .

Es decir, los puntos 1° y 2° del procedimiento general son importantes y nunca son tan sencillos como en el ejemplo del coche. Una vez que tenemos una descripción clara, precisa y completa de una función combinacional, es relativamente sencillo encontrar el circuito que la realiza físicamente. Así, en el ejemplo del coche la función sería:  $y = x_1 x_2 x_3 \overline{x_4}$ . No sólo aparecen dificultades a la hora de asignar variables lógicas a frases del lenguaje natural ("puerta abierta o cerrada", "luces encendidas", "motor en marcha", …) sino que también aparecen dificultades en la tarea de síntesis digital a la hora de obtener un conjunto completo de especificaciones funcionales claras, precisas e inequívocas (un "algoritmo") del método adecuado para resolver una tarea. Por ejemplo:

- 1. Diseñar un circuito que realice operaciones aritméticas en coma flotante para palabras de 16 bits.

- 2. Diseñar un multiplicador en complemento a 2 de alta velocidad.

Estas descripciones iniciales están más próximas a la lógica y a la teoría de autómatas que a las

del ejemplo del coche pero necesitan mucho conocimiento sobre formas de representación de números positivos y negativos, distintos algoritmos de multiplicación, etc... Su estudio, hasta conocer los circuitos intermedios básicos, es objeto de la Electrónica Digital. A partir de un cierto momento, cuando estos circuitos se integran en arquitecturas más complejas, su estudio corresponde a la Arquitectura de Computadores o a las otras grandes áreas de aplicación de la Electrónica Digital: Comunicación, Control e Instrumentación.

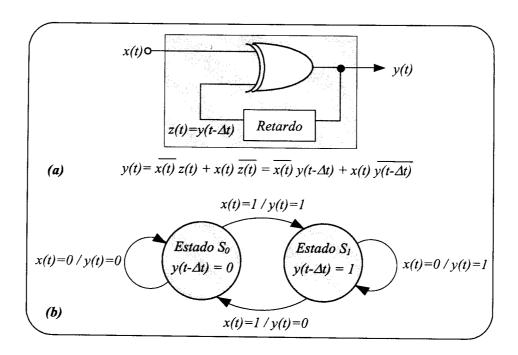

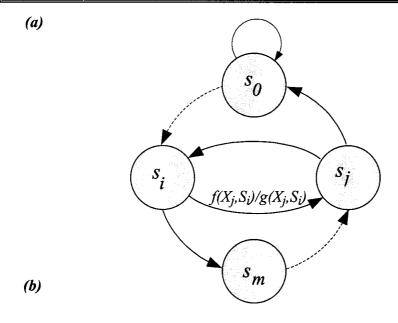

Hemos visto una primera justificación de las necesidades computacionales en lógica combinacional. Sin embargo, hay otro gran apartado de necesidades de computación en las que es imprescindible introducir el tiempo como variable de cálculo. A los circuitos correspondientes se les llama circuitos secuenciales y su modelo matemático es la Teoría de Autómatas Finitos. Representan aquellas situaciones en las que para calcular la respuesta de un sistema en un cierto instante,  $t = t_n$ , no basta con conocer las entradas en ese instante, sino que necesitamos conocer su "estado" y por consiguiente sus entradas y salidas en instantes anteriores. Decimos entonces que el sistema tiene "memoria".

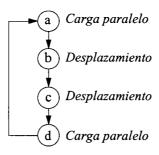

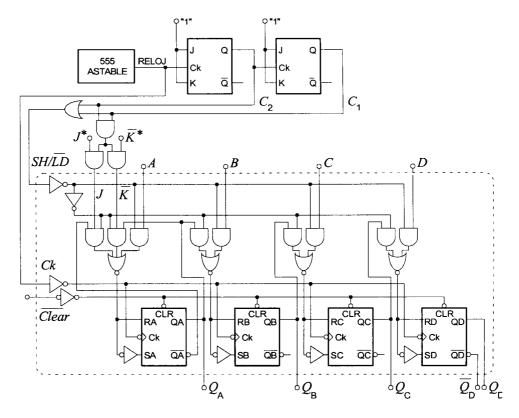

Ejemplos de funciones secuenciales básicas en la electrónica digital son, entre otros:

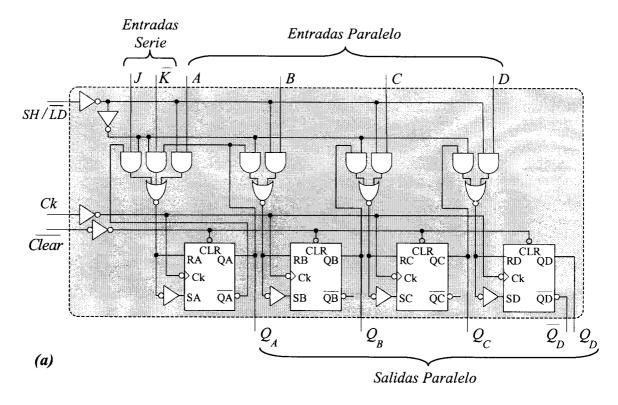

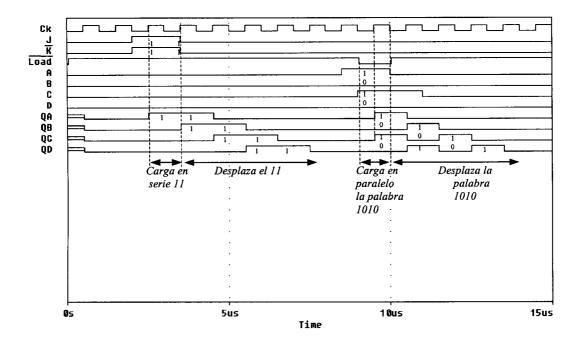

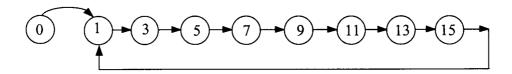

- **b.1.** Contadores.

- b.2. Registros de desplazamiento.

- **b.3.** Temporizadores

- **b.4.** Memorias RAM.

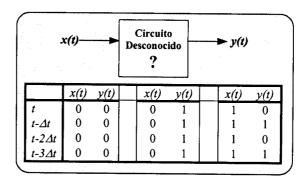

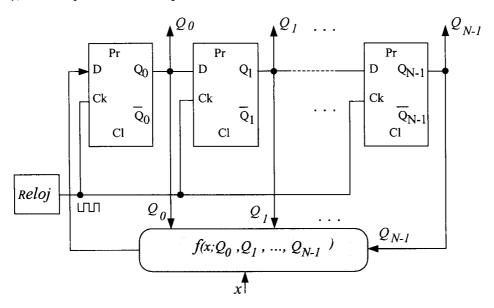

Para la síntesis de estas funciones secuenciales necesitamos los mismos operadores que usamos en la lógica combinacional, más la representación computacional del retardo. Es decir, una función  $Q(t_n)$  que coincide con el valor de la entrada, D, en el instante anterior

$$Q(t) = D(t - \Delta t)$$

o bien  $Q(t_n) = D(t_{n-1})(*)$

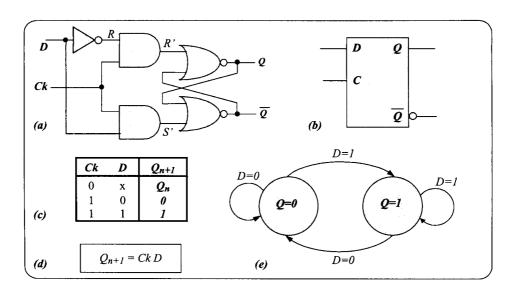

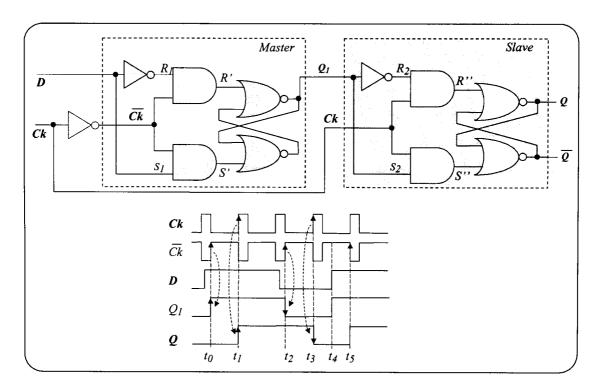

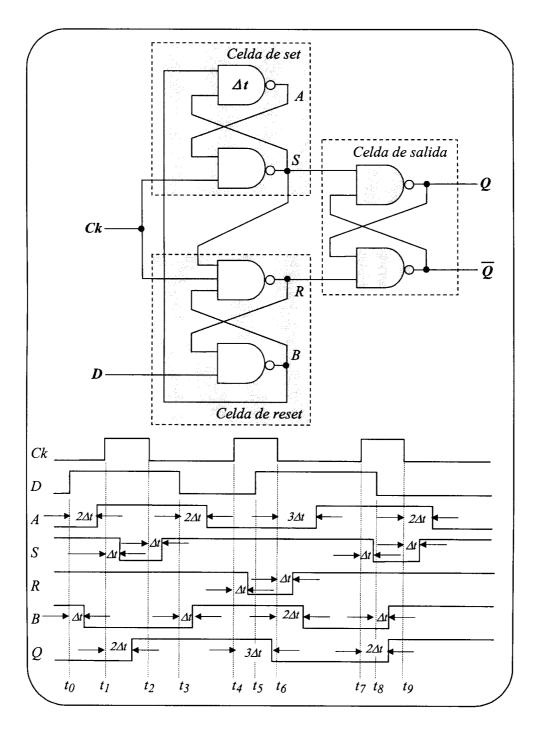

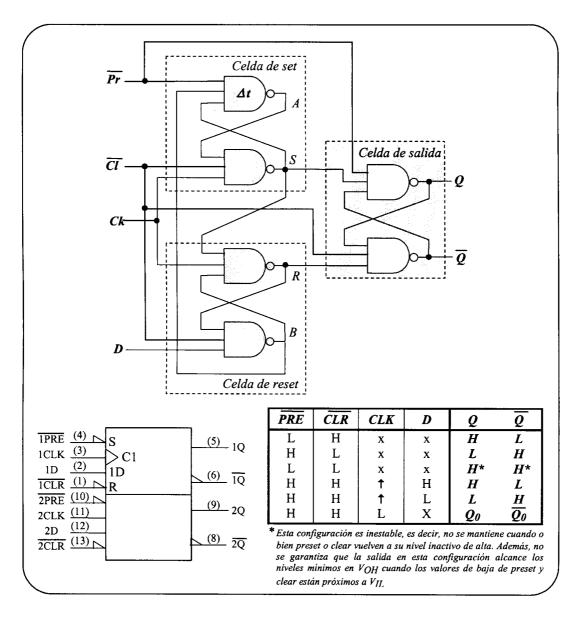

Esta función la realiza un circuito biestable tipo D (de "Delay"). Existen otros tipos de

<sup>(\*)</sup> A lo largo del texto usaremos de forma indistinta una u otra notación. En algunas ocasiones para simplificar también usaremos Q<sub>n</sub>=D<sub>n-1</sub>. Es decir, D(t-Δt), D(t<sub>n-1</sub>) y D<sub>n-1</sub> significan lo mismo: el valor de D en el instante de tiempo anterior al que se está considerando en este momento.

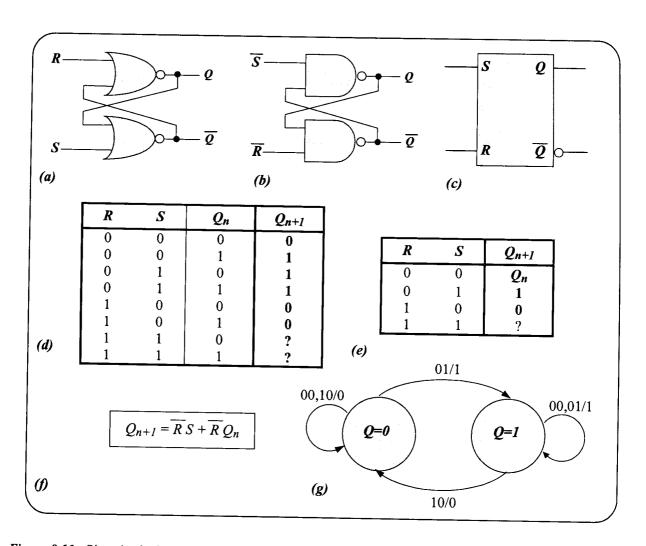

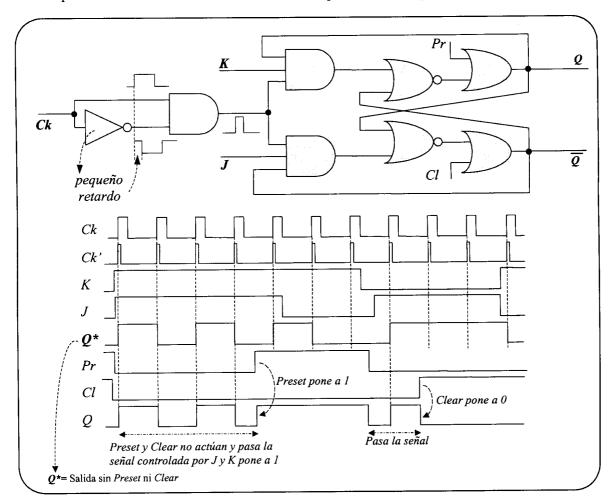

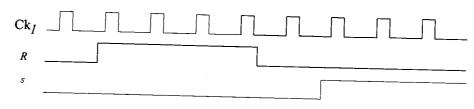

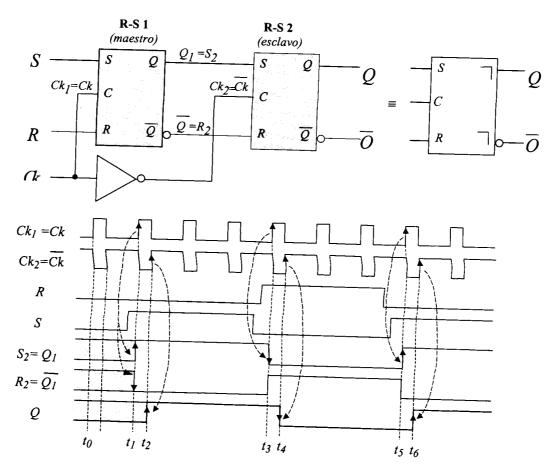

biestables (T, R-S y J-K) que incluyen también el retardo pero con funciones de disparo diferentes.

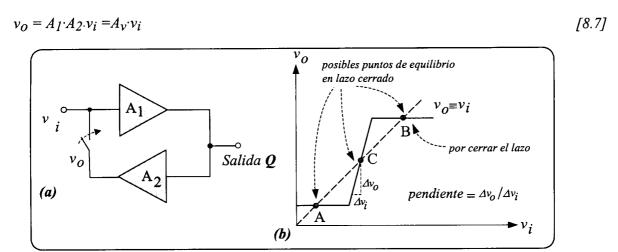

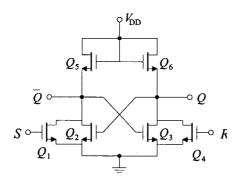

Veremos en su momento que estos circuitos biestables se pueden realizar mediante el acoplo de dos inversores con realimentación positiva, haciendo que siga siendo cierto que toda la electrónica digital se puede sintetizar con un único tipo de operador.

Seguimos avanzando en la contestación a la pregunta que daba título a este apartado. Es decir, estamos enumerando el conjunto de funciones necesarias para la representación, análisis y síntesis de sistemas digitales. Una relación de esas necesidades, razonablemente completa, debería incluir al menos a las siguientes:

- a) Funciones combinacionales, cuyo modelo matemático es el álgebra de Boole que vamos a estudiar a continuación.

- b) Funciones secuenciales, cuyo modelo matemático es la teoría de autómatas que estudiaremos más adelante, para aproximarla al tema en el que se usa.

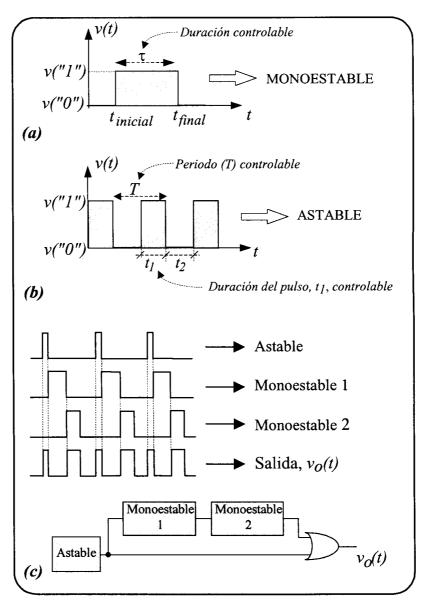

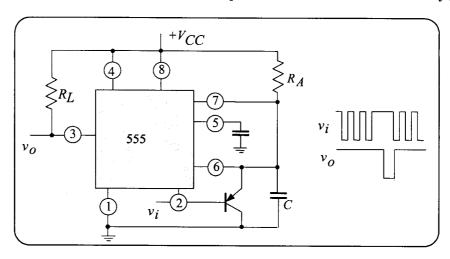

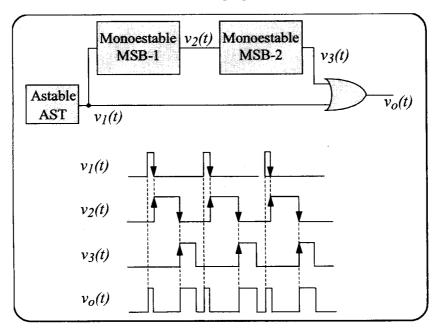

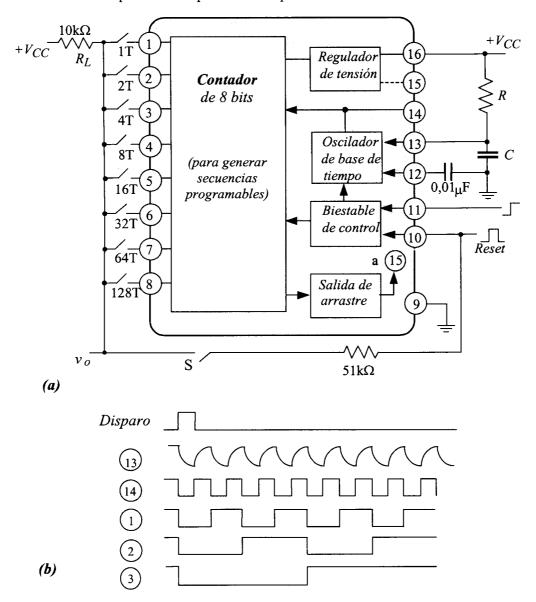

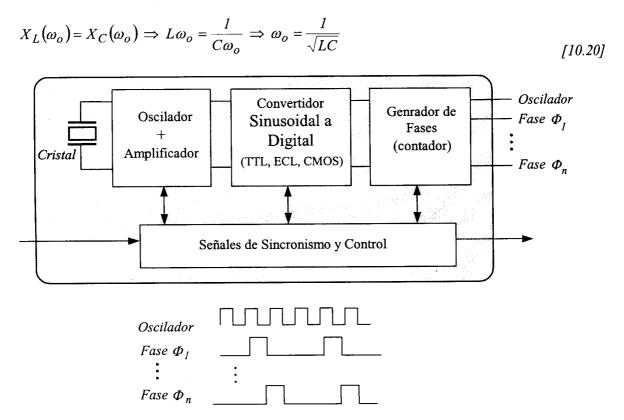

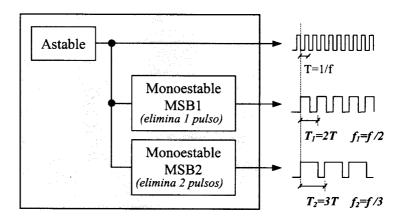

- c) Funciones de temporización, tanto síncronas como asíncronas, necesarias para engarzar en coorden todas las operaciones combinacionales y secuenciales que constituyen un sistema digital. Ejemplos de funciones de temporización son:

- c.1. Monoestables

- **c.2.** Osciladores astables.

- **c.3.** Temporizadores programables.

- **c.4.** Relojes monofásicos y polifásicos.

Una vez que tenemos el panorama aproximado de las funciones necesarias para la síntesis de sistemas digitales, dedicaremos el resto del tema al estudio de las bases matemáticas y el resto del libro al estudio de esas funciones siguiendo un criterio de complejidad creciente.

#### 1.3. VARIABLES Y OPERADORES LÓGICOS: ÁLGEBRA DE BOOLE

Tal como hemos desarrollado en extenso en el apartado anterior, toda la electrónica digital se basa en el uso de variables binarias y operadores lógicos para representar, transformar, almacenar y recuperar información. El modelo matemático soporte es el álgebra de Boole y la meta final será encontrar realizaciones físicas en distintas tecnologías electrónicas de sus operadores básicos.

El álgebra de Boole fue desarrollada inicialmente para el estudio formal del lenguaje. En su libro "Las Leyes del Pensamiento" decía George Boole que todas la operaciones del lenguaje, considerado como soporte del razonamiento, pueden hacerse computacionales mediante un sistema de símbolos compuesto por los siguientes elementos:

- a) Símbolos literales, (X, Y, Z,...), que representan cosas, como sujetos de nuestras concepciones.

- b) Símbolos de operación, como (+, •, complemento), que representan operaciones mentales por medio de las cuales combinamos los conceptos o formamos nuevos conceptos referentes a los mismos elementos.

- c) El signo de identidad (=).

Estos símbolos están sujetos a leyes bien definidas que C.E. Shannon en 1938 y en su trabajo "Un Análisis Simbólico de los Circuitos con Redes", asocia a representaciones físicas en términos de niveles de tensión y circuitos conmutadores que conducen o no conducen. Nace así la Teoría de la Conmutación y con ella el puente entre la lógica formal y su realización física mediante circuitos electrónicos combinacionales o secuenciales.

Veamos ahora un resumen del Álgebra de Boole de dos valores de clase  $B = \{0,1\}$ . Si sobre un conjunto de variables binarias (X, Y, Z,...) definimos las operaciones de suma lógica (+), producto lógico  $(\cdot)$  y complementación (inversión), el conjunto queda dotado de las estructura del Álgebra de Boole si cumple los siguientes postulados:

**P.1.** Las operaciones (+ y ·) son operaciones cerradas. El resultado de aplicarlas a cualesquiera de las variables del conjunto, producirá variables del conjunto.

**P.1.a:** Si

$$X \in B \notin Y \in B$$

, entonces  $(X+Y) \in B$

**P.1.b:** Si  $X \in B \notin Y \in B$ , entonces  $(X \cdot Y) \in B$

P.2. Existen elementos neutros para ambas operaciones ("0" para la suma y "1" para el producto).

**P.2.a:**

$$X + 0 = X$$

**P.2.b:**  $X \cdot 1 = X$

**P.3.** Ambas operaciones son conmutativas:

**P.3.a:**

$$X + Y = Y + X$$

**P.3.b:**

$$X \cdot Y = Y \cdot X$$

[1.5]

P.4. Ambas operaciones son distributivas, una respecto de la otra:

**P.4.a:**  $X + Y \cdot Z = (X + Y) \cdot (X + Z)$  (La suma es distributiva respecto al producto)

**P.4.b:**

$$X(Y + Z) = X \cdot Y + X \cdot Z$$

(El producto es *distributivo* respecto a la suma)

[1.6]

**P.5.** Complementariedad. Para cada variable X existe su complementaria  $\overline{X}$  y entre ambas se cumplen las siguientes condiciones:

**P.5.a:**

$$X + \overline{X} = 1$$

**P.5.b:**

$$X \cdot \overline{X} = 0$$

[1.7]

**Ejercicio:** Demostrar que "el producto es distributivo respecto de la suma".

#### Solución:

Su expresión lógica es:

$$X(Y+Z) = XY+XZ ag{1.8}$$

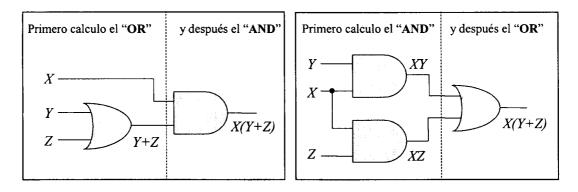

Podríamos demostrarlo por inducción completa, poniendo las tablas de verdad de ambas expresiones supuestamente equivalentes y viendo después que los dos circuitos correspondientes también son equivalentes: Las *figuras 1.5* muestra las tablas de verdad y la 1.6 los circuitos correspondientes a las expresiones lógicas de ambos lados del igual.

Obsérvese que la columna correspondiente a la parte izquierda del igual, X(Y+Z), y la correspondiente a la parte derecha, XY+XZ, son iguales. También los circuitos nos muestran el

carácter intercambiable del orden de las variables para las operaciones OR y AND.

| X           | Y | Z | Y+Z | X(Y+Z) | XY | XZ | XY+XZ |

|-------------|---|---|-----|--------|----|----|-------|

| 0           | 0 | 0 | 0   | 0      | 0  | 0  | 0     |

| 0           | 0 | 1 | 1   | 0      | 0  | 0  | 0     |

| 0           | 1 | 0 | 1   | 0      | 0  | 0  | 0     |

| 0           | 1 | 1 | 1   | 0      | 0  | 0  | 0     |

| 1           | 0 | 0 | 0   | 0      | 0  | 0  | 0     |

| 1           | 0 | 1 | 1   | 1      | 0  | 1  |       |

| 1           | 1 | 0 | 1   | - 1    | 1  | 0  | 1     |

| 1           | 1 | 1 | 1   | 1      | 1  | 1  | 1     |

| son iguales |   |   |     |        |    |    |       |

Figura 1.5. Tablas de verdad para demostrar la distributividad del producto respecto de la suma.

Figura 1.6. Circuitos funcionalmente equivalentes.

De forma análoga podríamos demostrar que también la suma es distributiva respecto del producto. Es decir, que X+YZ=(X+Y)(X+Z).

Una propiedad importante del álgebra de Boole es la *dualidad*. Cada miembro de un par dual, por ejemplo X+0=X, se puede obtener del otro miembro del par,  $(X \cdot I=X)$ , intercambiando los elementos "0" y "1" y los operadores suma por producto y viceversa. Si una relación es cierta, también lo será su dual.

Los operadores suma y producto y la complementación han sido definidos en el apartado anterior mediante sus tablas de verdad. Esta es una definición en extenso, es decir describimos la función realizada por un operador listando el conjunto de todas las configuraciones de valores posibles en sus variables de entrada y viendo cual es la respuesta a cada una de esas configuraciones. Esta forma de definir los operadores nos permite usar el procedimiento de inducción completa para demostrar los postulados P.2, P.3, P.4 y P.5 y para pronunciarnos acerca de la verdad o falsedad de cualquier otra relación.

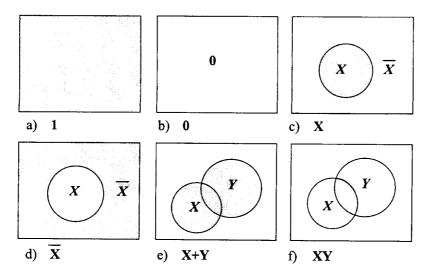

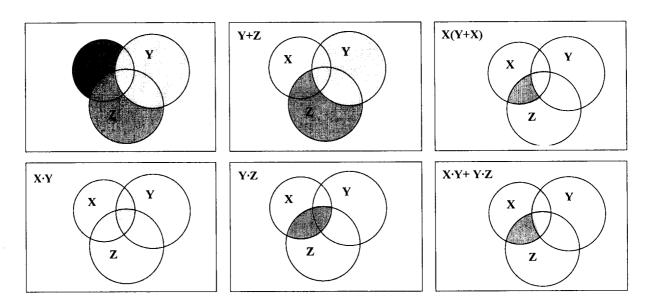

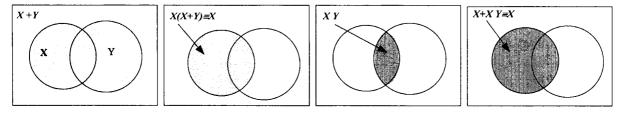

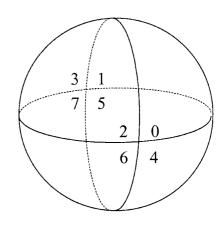

La otra forma usual y sencilla de demostrar la verdad o falsedad de una determinada relación lógica para expresiones con pocas variables es usar los diagramas de Venn, basados en la unión e intersección de conjuntos. A cada variable se le asocia un área matizada dentro de un rectángulo. Su complementaria es el resto del rectángulo, de forma que el área del rectángulo representa la unidad. La figura 1.7 ilustra el procedimiento, para la negación de una variable,  $(\overline{X})$ , la suma (X+Y) que incluye el área que pertenece a X  $\hat{\mathbf{o}}$  pertenece a Y, y el producto (X-Y) que sólo incluye el área que pertenece a X  $\mathbf{v}$  a Y. Si dos expresiones son iguales deben de generar la misma área matizada.

Figura 1.7. Diagramas de Venn

Veamos ahora el mismo ejemplo de distributividad respecto a la suma usando los diagramas de Venn. Es decir, veamos que X(Y+Z) produce la misma área matizada que XY+XZ. La figura 1.8 ilustra el proceso:

Figura 1.8. Demostración de distributividad del producto respecto de la suma mediante diagramas de Venn.

A partir de los postulados **P.1**, ..., **P.5**, enunciados anteriormente, pueden enunciarse y demostrarse un conjunto de *teoremas*, entre los que podemos destacar los siguientes:

| Teoremas                   |                                                                                                           |  |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| T.1: Doble complementación | $\overline{\overline{X}} = X$                                                                             |  |  |  |  |  |

| T.2: Idempotencia          | $X+X=X$ $X\cdot X=X$                                                                                      |  |  |  |  |  |

| T.3: Absorción             | $X+X\cdot Y = X$ $X\cdot (X+Y) = X$                                                                       |  |  |  |  |  |

| T.4: Adyacencia            | $X \cdot Y + X \cdot \overline{Y} = X$ $(X + Y) \cdot (X + \overline{Y}) = X$                             |  |  |  |  |  |

| T.5: Teoremas de DeMorgan: | $\overline{X + Y} = \overline{X} \cdot \overline{Y}$ $\overline{X \cdot Y} = \overline{X} + \overline{Y}$ |  |  |  |  |  |

Veamos ahora, recordando los cinco postulados del Álgebra de Boole, cómo podemos

demostrar algunos de estos teoremas.

Ejercicio: Demostrar el teorema de "absorción".

#### Solución:

Las expresiones lógicas del teorema de absorción son:

$$X+XY=X \quad y \quad X(X+Y)=X \tag{1.9}$$

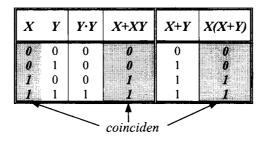

Podemos demostrar este teorema mediante los tres procedimientos vistos anteriormente. Es decir, por tablas de verdad, por aplicación directa de los postulados y mediante diagramas de Venn.

#### a) Por tablas de verdad

Figura 1.9. Demostración del teorema de absorción mediante tablas de verdad.

Obsérvese como coinciden las columnas correspondientes a X con las correspondientes a X+XY y X(X+Y).

- Por aplicación directa de los postulados

Sacando a la variable X como factor común. Así, X+XY=X(1+Y) = X, puesto que 1+Y=1.

- c) Por diagramas de Venn:

Figura 1.10. Demostración del teorema de absorción mediante diagrams de Venn.

Si pensamos en términos de circuitos, la demostración también es evidente, puesto que a la puerta "OR" de salida llegan X y el producto XY, que siempre es más restrictivo que sólo X.

Figura 1.11. Demostración mediante el circuito que implementa la expresión lógica del teorema de absorción.

Dejamos para el alumno la demostración de la expresión dual X(X+Y)=X.

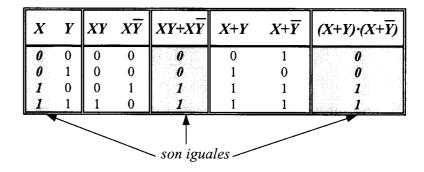

Ejercicio: Demostrar el teorema de adyacencia

#### Solución:

El teorema de adyacencia se pone de manifiesto mediante las siguientes expresiones:

$$XY + X\overline{Y} = X$$

$y$   $(X + Y) \cdot (X + \overline{Y}) = X$  [1.10]

Ya deberíamos saber actuar sin mucho pensamiento: ponemos las tablas de verdad o dibujamos los diagramas de Venn o aplicamos directamente los postulados y después podemos implementarlo dibujando los circuitos.

Veámoslo mediante las tablas de verdad.

Figura 1.12. Demostración de los teoremas de adyacencia.

Como podemos observar las tres columnas coinciden. Veamos ahora los circuitos que implementan ambas funciones.

Figura 1.13. Implementación de los teoremas de adyacencia.

Obsérvese que el paso de una expresión a su *dual* sólo ha permutado la posición de los circuitos AND con la de los OR.

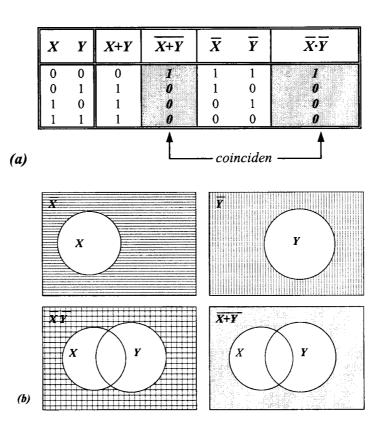

El primero de los teoremas de DeMorgan lo vamos a demostrar por inducción completa y el segundo gráficamente, mediante el uso de diagramas de Venn. Los resultados se muestran en la figura 1.14. En 1.14.a, hemos escrito las cuatro configuraciones lógicas asociadas a las dos variables X e Y (00, 01, 10, 11) y los estados lógicos correspondientes a (X+Y),  $(\overline{X+Y})$ ,  $\overline{X}$ ,  $\overline{Y}$  y  $\overline{X} \cdot \overline{Y}$  Obsérvese que la columna correspondiente a  $\overline{X+Y}$  coincide con la correspondiente a  $\overline{X} \cdot \overline{Y}$ , con lo que queda demostrada la igualdad de ambas expresiones:  $\overline{X+Y} = \overline{X} \cdot \overline{Y}$ .

Por otro lado, en la *figura 1.14.b* se parte de las áreas asociadas a X e Y y se construyen las áreas asociadas a  $\overline{X}$ ,  $\overline{Y}$ ,  $X \cdot Y$  y  $\overline{X+Y}$ . Obsérvese como el área rayada asociada a  $\overline{X+Y}$  es la misma que la que corresponde a  $\overline{X} \cdot \overline{Y}$ .

Figura 1.14. Demostración de los Teoremas de Morgan. (a) Por inducción completa. (b) Por diagramas de Venn.

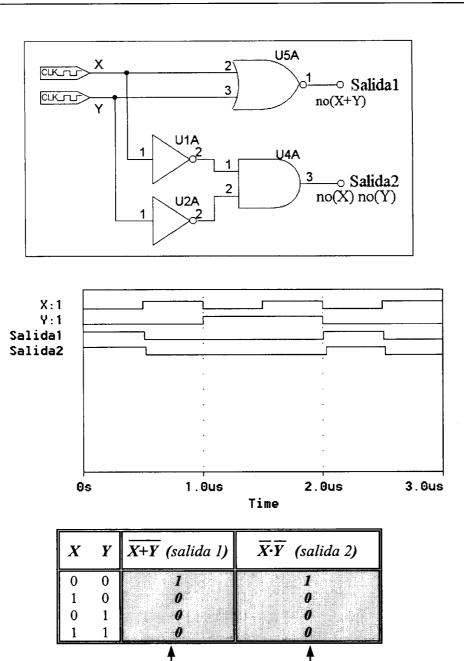

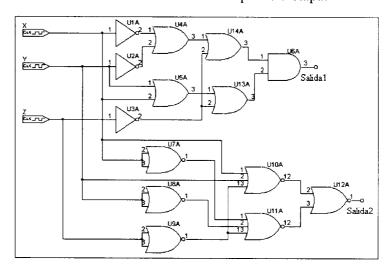

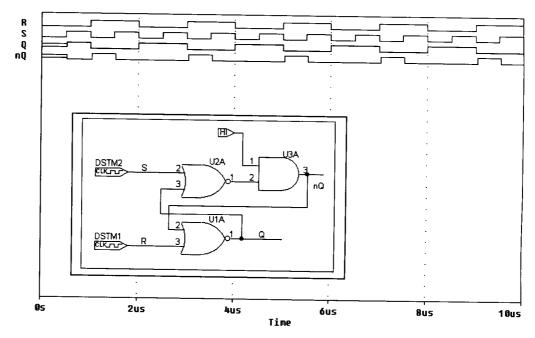

**Ejercicio:** Usar un simulador para comprobar que las respuestas correspondientes a los circuitos de ambos lados del igual,  $(\overline{X} + \overline{Y}) y (\overline{X} \cdot \overline{Y})$ , coinciden

#### Solución:

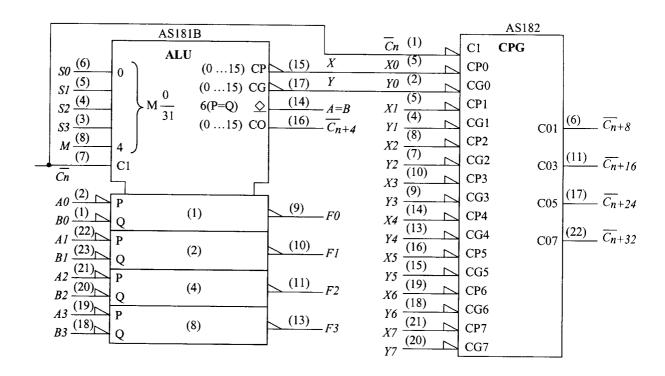

En la simulación, para generar de forma automática la tabla de verdad del circuito, usamos como señales de entrada dos relojes cuyas frecuencias son una el doble de la otra, así tenemos las cuatro configuraciones posibles para las dos variables X e Y. Hemos tomado para X una frecuencia de 1MHz y para Y una frecuencia de 2MHz. La figura 1.15 muestra las tablas de verdad, el circuito y el cronograma correspondiente a  $\overline{X+Y}=\overline{X}\cdot\overline{Y}$ .

Figura 1.15. Simulación de los circuitos  $\overline{X+Y}$  y  $\overline{X}\cdot\overline{Y}$  (leyendo en vertical los valores de las variables del cronograma, comprobamos la tabla de verdad)

- coinciden

#### 1.4. FUNCIONES LÓGICAS: FORMAS CANÓNICAS

Un conjunto de variables lógicas conectadas por cualquier combinación de los operadores básicos (suma, producto y complementación) constituye una función lógica. Más formalmente, una función lógica, f, de n variables,  $(x_1, x_2, ...x_n)$ , sobre un álgebra de Boole  $B = \{0,1\}$ , es cualquier aplicación del producto cartesiano de B por sí mismo n veces,  $B^n$ , en B.

$$\begin{array}{c}

\stackrel{n}{\longleftarrow} \\

B^n = B \times B \times \dots \times B \\

B^n \xrightarrow{f(x_1, \dots, x_n)} B

\end{array}$$

Los elementos de  $B^n$  son configuraciones lógicas de n variables. Para n=2, tenemos cuatro configuraciones ( $x_1 = 0$ ,  $x_2 = 0$ ;  $x_1 = 0$ ,  $x_2 = 1$ ;  $x_1 = 1$ ,  $x_2 = 0$ ;  $x_1 = 1$ ,  $x_2 = 1$ ). En general, para n variables tendremos  $2^n$  configuraciones mutuamente exclusivas. Como para cada una de estas configuraciones la función lógica puede asignarle un "1" ó un "0", tenemos  $2^{2^n}$  funciones lógicas posibles.

De las distintas formas de representar estas funciones vamos a comentar las más significativas desde el punto de vista electrónico.

- 1. Forma normal disyuntiva (suma de términos mínimos).

- 2. Forma normal conjuntiva (producto de términos máximos).

- **3.** Forma NAND.

- 4. Forma NOR.

Por sencillez en la presentación y sin ninguna pérdida de generalidad nos referiremos en todos los casos a funciones de dos variables  $(x_1, x_2)$ .

#### 1.4.1. Forma Normal Disyuntiva

La forma normal disyuntiva expresa una función lógica como suma de productos. Cada producto contiene a todas las variables, negadas o sin negar, sin repetirse ninguna. A los productos se les llama términos mínimos ("minterms") porque ocupan áreas mínimas (intersecciones) en los diagramas de Venn y se corresponden con las filas de la tabla de verdad, que a su vez son las distintas

configuraciones de valores posibles en las variables de entrada, interpretadas asociando al valor "0" la variable complementada y al valor "1" la variable sin complementar. Así, la configuración 0 1 se asocia al término mínimo  $\overline{x_1} x_2$  porque si hacemos  $x_1 = 0$  y  $x_2 = 1$  sólo ese producto tendrá el valor 1  $(\overline{x_1} x_2 = \overline{0} \cdot 1 = 1 \cdot 1 = 1)$ . Todos los demás productos  $(\overline{x_1} \overline{x_2}, x_1 \overline{x_2}, y_1 \overline{x_2})$  son cero para esos valores de las variables de entrada  $(x_1 = 0 \text{ y } x_2 = 1)$ . Sea cual fuere el valor de la configuración de entrada, sólo hay un término mínimo distinto de cero. Como estas configuraciones son mutuamente exclusivas, toda función lógica puede expresarse como suma lógica de las configuraciones que la activan. Así, para dos variables tenemos,

$$f_{m}(x_{1},x_{2}) = f(0,0)\bar{x}_{1}\bar{x}_{2} + f(0,1)\bar{x}_{1}x_{2} + f(1,0)x_{1}\bar{x}_{2} + f(1,1)x_{1}x_{2} =$$

$$= a_{0}\bar{x}_{1}\bar{x}_{2} + a_{1}\bar{x}_{1}x_{2} + a_{2}x_{1}\bar{x}_{2} + a_{3}x_{1}x_{2} = \sum_{i=0}^{2^{n}-1} a_{i}m_{i}$$

[1.12]

siendo

$$a_i \in \{0,1\}$$

y  $m_i = x_1^p x_2^q$ ,  $i = (p,q)$   $(p,q) \in \{0,1\}$  con la notación de Gilstrap  $(x^0 = \overline{x}, x^1 = x)$

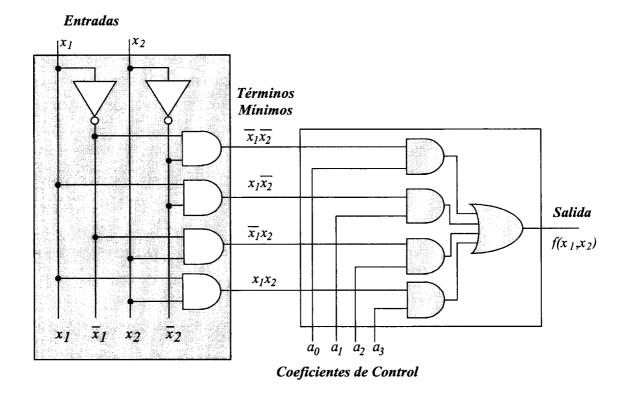

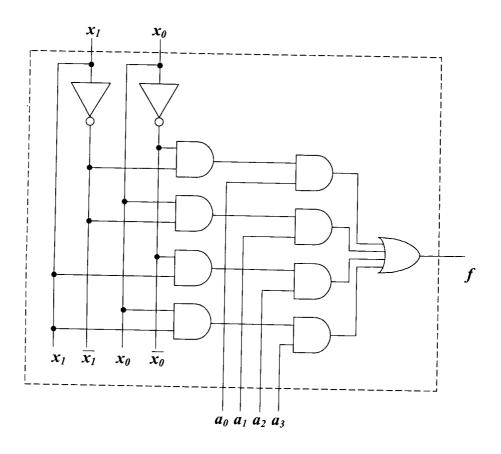

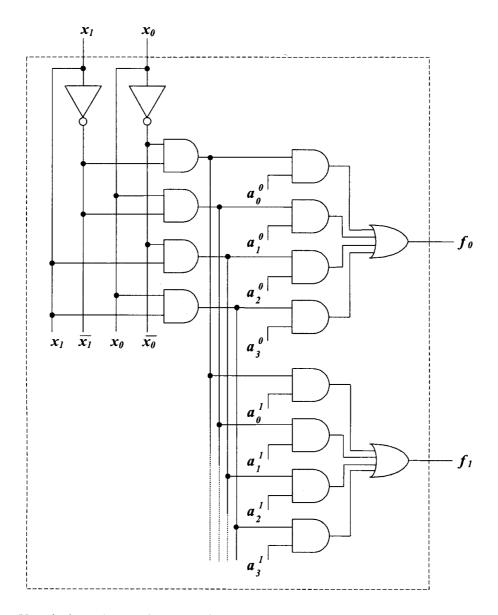

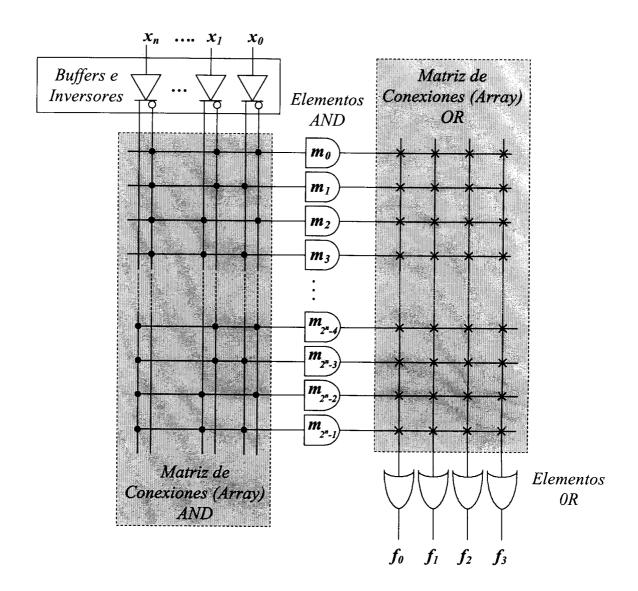

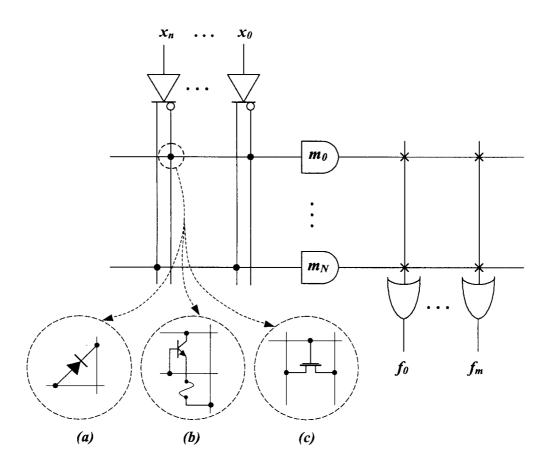

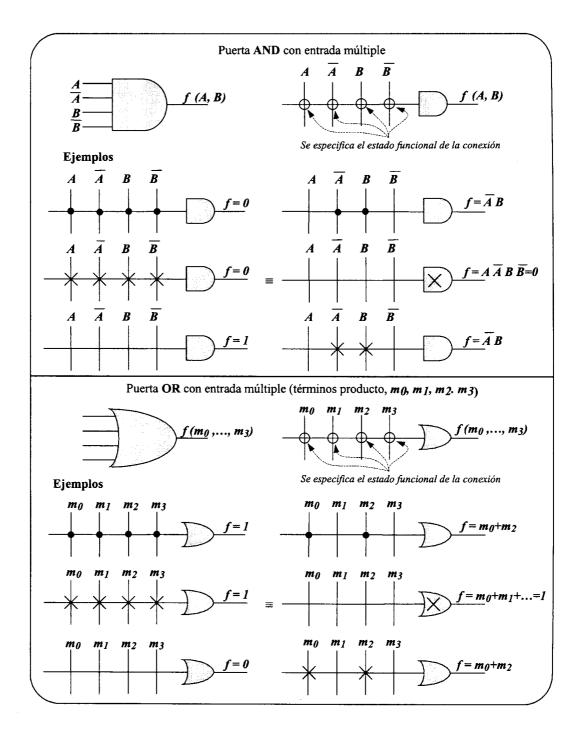

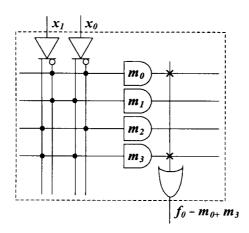

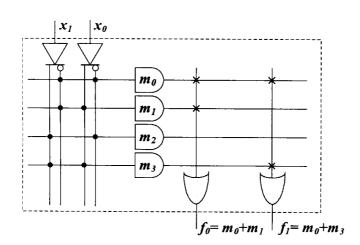

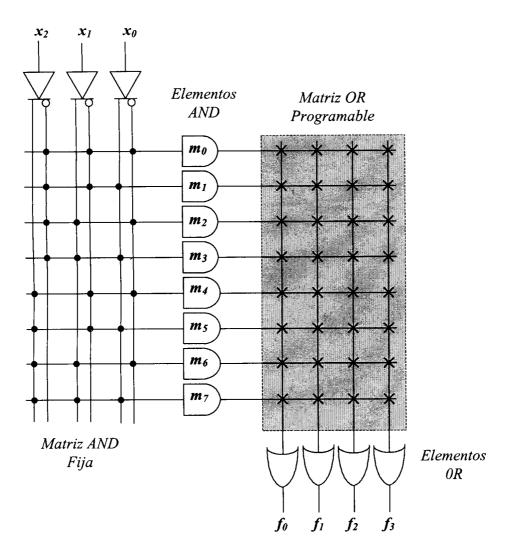

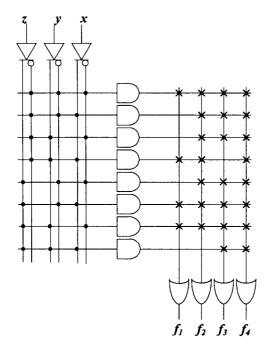

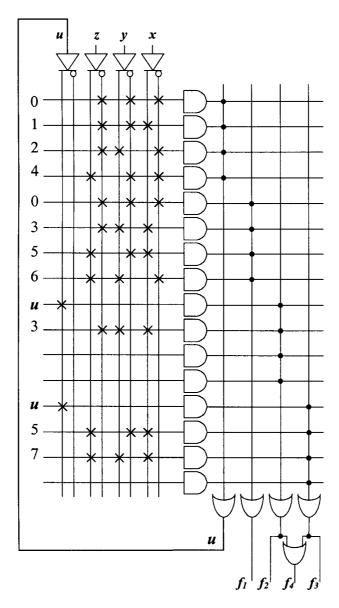

Cada forma de representar una función lógica sugiere su procedimiento de síntesis. Así, en la forma normal disyuntiva que hemos visto aparecen productos de todas las variables  $(x_1, x_2)$  y sus negadas  $(x_1, x_2)$  para formar los cuatro términos mínimos  $(m_0 = x_1 x_2)$ ,  $m_1 = x_1 x_2$ ,  $m_2 = x_1 x_2$  y  $m_3 = x_1 x_2$ ). Después estos términos mínimos se tienen que multiplicar por los coeficientes  $(a_0, a_1, a_2, a_3)$  que determinan si van a pertenecer o no a una función concreta. Finalmente, los nuevos productos  $(a_i m_i)$  se suman lógicamente. Si vamos construyendo el circuito que representa los procesos que hemos descrito tenemos la realización física de la expresión general de las funciones lógicas de dos variables, tal como se ilustra en la figura 1.16. Obsérvese que esta es una función lógica universal de forma que al variar los valores de los coeficientes  $\{a_i\}$  desde (0000) hasta (1111) vamos obteniendo las 16 funciones lógicas de dos variables que se incluyen en la parte inferior de la figura. Véase también que el subíndice decimal (i) de la función  $(f_i)$  pasado a binario genera el valor de los coeficientes  $\{a_i\}$  que sintetizan la función. As(i) es la función AND porque 1 en binario es 0001  $(a_0 = a_1 = a_2 = 0, a_3 = 1)$  lo que supone que la función sólo posee el término mínimo  $m_3$  (1), o sea el correspondiente a  $x_1 x_2$ . Análogamente  $f_2$  es la función coincidencia que sólo se activa cuando las dos entradas son iguales, porque el decimal 9 en binario es 1001, es decir  $a_0 = 1$ ,

$a_1 = a_2 = 0$ ,  $a_3 = 1$ . Posee por consiguiente los términos mínimos  $m_0(\bar{x}_1 \bar{x}_2)$  y  $m_3(x_1 x_2)$ .

| $x_1$ | $x_2$ | $m_i$ | $a_i$                 | <b>f</b> 0 | $f_I$ | $f_2$ | <b>f</b> 3 | **** | <b>f</b> 9 | •••• | <b>f</b> 14 | $f_{15}$ |

|-------|-------|-------|-----------------------|------------|-------|-------|------------|------|------------|------|-------------|----------|

| II .  | 0     |       |                       |            |       |       |            | •••• |            |      | 1           | 1        |

|       | 1     |       |                       |            |       |       |            |      |            |      |             |          |

| 38    | 0     |       | 1 1                   | I          |       |       |            |      |            |      |             | 1        |

| 1     | 1     | $m_3$ | <i>a</i> <sub>3</sub> | 0          | 1     | 0     | 1          |      | 1          | •••• | 0           | 1        |

Figura 1.16. Función universal para dos variables  $(x_1, x_2)$  en forma normal disyuntiva y valor de los coeficientes  $\{a_i\}$  que la proyectan en cada una de las 16 funciones posibles para dos variables

#### 1.4.2. Forma Normal Conjuntiva

En la forma normal disyuntiva que acabamos de ver, las funciones lógicas se representan mediante una suma de productos, a los que llamábamos términos mínimos (minterms) porque al representarlos en diagrama de Venn daban lugar a áreas mínimas (intersecciones entre áreas asociadas a variables o a sus negadas). Esta representación era completa y quedaba caracterizada por un vector de coeficientes  $\{a_i\}$  que nos decían cuáles eran los términos mínimos,  $\{m_i\}$ , que participaban en una determinada función. Es decir aquellos cuya presencia en la entrada de un circuito lógico hacían que su salida fuera "1". Finalmente, los términos mínimos se asociaban a filas de la tabla de verdad (a configuraciones de entrada mutuamente exclusivas) con la interpretación siguiente: Un cero corresponde a una variable negada y un uno a una variable sin negar. Así, (0 1) corresponde a  $\overline{x_1}$   $x_2$ , por ejemplo.

Vamos a ver ahora una representación dual, en la que cualquier función lógica puede representarse como producto de sumas, a las que llamamos términos máximos (maxterms) porque al representarlos en diagramas de Venn dan lugar a áreas máximas (uniones de las áreas correspondientes a variables individuales o a sus negadas). Veremos que esta representación también es completa y queda caracterizada por un vector de coeficientes,  $\{A_i\}$ , que nos dicen cuáles son los términos máximos,  $\{M_i\}$  que participan en una determinada función. Como ahora los coeficientes,  $A_i$ , entran sumando, son relevantes aquellos términos máximos,  $M_i$ , cuyo  $A_i$  correspondiente sea cero. La suma de cualquier término lógico con "1" es "1" y el producto de "1" por cualquier término reproduce ese término, de forma dual a como ocurría con los productos y sumas en la representación por minterms.

Veamos ahora cómo se construyen los maxterms a partir de las  $2^n$  filas de la tabla de verdad de una función de n variables lógicas. Por razones pedagógicas y sin pérdida de generalidad usaremos como ilustración el caso de dos variables,  $(x_1, x_2)$ . La tabla de la figura 1.17 muestra las cuatro configuraciones posibles (00, 01, 10, 11), los maxterms asociados  $(M_0, M_1, M_2, M_3)$  y los coeficientes que designan la presencia o ausencia de cada uno de esos maxterms en una función.

Obsérvese que cada maxterm representa a una única fila de la tabla de verdad y una variable de entrada se complementa cuando su valor en la configuración de salida es "1" y no se complementa cuando su valor en esa fila es "0". Así, a (00) le corresponde el maxterm  $M_0 = x_1 + x_2$ , a (01) el  $M_1 = x_1 + x_2$ , a (10) el  $M_2 = x_1 + x_2$  y a (11) el  $M_3 = x_1 + x_2$ .

| $x_1$ | $x_2$ | Maxterms                          | Coeficientes |

|-------|-------|-----------------------------------|--------------|

| 0     | 0     | $x_1+x_2$                         | $M_0$        |

| 0     | 1     | $x_1 + \overline{x_2}$            | $M_{I}$      |

| 1     | 0     | $\overline{x}_1 + x_2$            | $M_2$        |

| 1     | 1     | $\overline{x}_1 + \overline{x}_2$ | $M_3$        |

Figura 1.17. Tabla de verdad correspondiente a los términos máximos (maxterms).

De nuevo en la definición de los maxterms vemos la dualidad con los minterms. Allí construíamos un minterm multiplicando las variables sin negar o negadas dependiendo que en la fila de la tabla de verdad apareciera un "1" ó un "0" y decíamos que al evaluar la expresión del minterm correspondiente a cada fila con los valores de esa fila obteníamos un uno.

Ahora, con los maxterms, al evaluar el valor de la expresión de un maxterm con los valores correspondientes a su fila, obtenemos un cero. Por ejemplo, el maxterm  $M_0 = x_1 + x_2$  sólo posee el valor cero si  $x_1 = 0$  y  $x_2 = 0$ . Análogamente,  $M_1 = x_1 + x_2$  sólo será cero si  $x_1 = 0$  y  $x_2 = 1$ , y así sucesivamente.

Como las cuatro configuraciones lógicas de la tabla son mutuamente exclusivas, sea cual fuere la configuración de entrada sólo habrá un maxterm distinto de 1, de forma dual a como sólo existía un minterm distinto de cero.

Por consiguiente y como consecuencia de esta exclusividad mutua, toda función lógica puede expresarse como producto lógico de maxterms. Llamando  $A_i$  a los coeficientes correspondientes a cada  $M_i$ , tenemos:

$$f_{M}(x_{1},x_{2}) = (A_{0} + M_{0})(A_{1} + M_{1})(A_{2} + M_{2})(A_{3} + M_{3})$$

[1.13]

que es generalizable de forma inmediata para funciones de n variables y  $2^n$  maxterms,

$$f_M(x_1, x_2) = \prod_{i=0}^{2^n - 1} (A_i + M_i)$$

[1.14]

En esta representación calculamos primero el OR de  $(A_i, M_i)$  y después el AND de esas sumas,

de forma dual a como hacíamos en la representación por minterms donde primero calculábamos el AND de  $(a_i, m_i)$  y después el OR de esos productos.

Allí, en minterms, sólo nos quedaban los  $m_i$  cuyos coeficientes  $a_i$  eran unos. Aquí, en maxterms, sólo nos quedan los  $M_i$  cuyos coeficientes  $A_i$  son cero. Así, el valor final de un producto de sumas sólo será cero si y sólo si el valor de todos los maxterms que contiene es cero. De otra forma, su valor será uno.

Dado que el subíndice usado para representar a los coeficientes es el decimal correspondiente a la expresión binaria de la configuración correspondiente ( $M_0$  para 00,  $M_1$  para 01, etc...), podemos representar de forma más compacta la función, usando sólo los subíndices de los maxterms que contiene. Así, si tiene  $M_0$ ,  $M_1$  y  $M_3$ , la función será

$$f_M(x_1, x_2) = \prod M(0, 1, 3)$$

[1.15]

siendo 0, 1 y 3 los decimales cuya representación binaria corresponde a las filas de la tabla para las que la función es cero.

Minterms y maxterms son dos representaciones alternativas (duales) de la tabla de verdad de una función lógica. Además, para una misma función, una forma de representación puede obtenerse de la otra por simples manipulaciones algebraicas usando los teoremas de DeMorgan, ya que cada maxterm (minterm) puede obtenerse complementando el minterm (maxterm) correspondiente.

Así, a

$$m_0 = \overline{x_1} \cdot \overline{x_2}$$

le corresponde  $M_0 = \overline{m_0} = \overline{x_1} \cdot \overline{x_2} = x_1 + x_2$  [1.16]

Análogamente,

$$M_1 = \overline{m_1} = \overline{x_1 \cdot x_2} = x_1 + \overline{x_2}$$

[1.17]

$$M_2 = \overline{m_2} = \overline{x_1 \cdot x_2} = \overline{x_1} + x_2$$

[1.18]

$$M_3 = \overline{m_3} = \overline{x_1 \cdot x_2} = \overline{x_1} + \overline{x_2}$$

[1.19]

La tabla de la *figura 1.18* resume las dos representaciones, por minterms y maxterms, para funciones de dos variables.

|       | Formas Canónicas |                                                       |                       |                                                          |              |  |  |  |  |  |

|-------|------------------|-------------------------------------------------------|-----------------------|----------------------------------------------------------|--------------|--|--|--|--|--|

| $x_l$ | $x_2$            | Minterms                                              | Coeficientes          | Maxterms                                                 | Coeficientes |  |  |  |  |  |

| 0     | 0                | $\overline{x_1} \cdot \overline{x_2} = m_0$           | $a_0$                 | $x_1 + x_2 = M_0 = \overline{m_0}$                       | $A_0$        |  |  |  |  |  |

| 0     | 1                | $\overline{x_1} \cdot x_2 = m_1$                      | $a_1$                 | $x_1 + \overline{x_2} = M_1 = \overline{m_1}$            | $A_I$        |  |  |  |  |  |

| 1     | 0                | $x_1 \cdot \overline{x_2} = m_2$                      | $a_2$                 | $\overline{x_1} + x_2 = M_2 = \overline{m_2}$            | $A_2$        |  |  |  |  |  |

| 1     | 1                | $x_1 \cdot x_2 = m_3$                                 | <i>a</i> <sub>3</sub> | $\overline{x_1} + \overline{x_2} = M_3 = \overline{m_3}$ | $A_3$        |  |  |  |  |  |

| Fun   | ción             | $f_m = \sum_i a_i \cdot$                              | $m_{i}$               | $F_{M} = \prod_{i} (A_{i} +$                             | $M_i$        |  |  |  |  |  |

|       |                  | $a_i=1$ si el minterm esta $a_i=0$ si no está present | •                     | $A_i$ =0 si el maxterm está $A_i$ =1 si no está presente | - I          |  |  |  |  |  |

Figura. 1.18. Minterms, maxterms, sus coeficientes y las formas canónicas correspondientes para funciones de dos variables,  $(x_1, x_2)$

**Ejercicio:** Obtener la representación por minterms y maxterms de las siguientes funciones de dos variables;

- a) Coincidencia

- b) Anticoincidencia (OR-exclusivo)

- c) NAND

- d) NOR

#### Solución

Escribamos la tabla de verdad para cada uno de los casos y en la representación por minterms nos quedamos con los unos y en la de maxterms con los ceros.

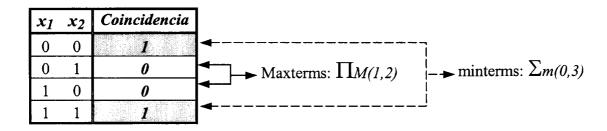

a) La figura 1.19 muestra la tabla de verdad para la coincidencia. En ella se han marcado las configuraciones correspondientes al resultado por minterms y por maxterms.

Figura 1.19. Tabla de verdad para la coincidencia

**b)**, **c)** y **d)** La tabla de verdad para las funciones X-OR, NAND y NOR es la que se muestra en la *figura 1.20*. Para representar estas funciones por minterms tomamos los términos mínimos que hacen 1 la función y para representar por maxterms la misma función tomamos los términos máximos que la hacen 0 (ver la última fila de la tabla).

| $x_1$    | $x_2$   | X-OR                   | NAND  | NOR            |  |

|----------|---------|------------------------|-------|----------------|--|

| 0        | 0       | 0                      | 1     | 1              |  |

| 0        | 1       | 1                      | 1     | 0              |  |

| 1        | 0       | 1                      | 1     | 0              |  |

| 1        | 1       | 0                      | 0     | 0              |  |

| Represer | ntación | 11                     |       | Ш              |  |

| poi      | r       | •                      | •     | <b>V</b>       |  |

| minterms |         | minterms $\sum m(1,2)$ |       | $\sum m(0)$    |  |

| Maxterms |         | $\Pi M(0,3)$           | Пм(3) | $\Pi M(1,2,3)$ |  |

Figura 1.20. Representación por minterms y por maxterms de las funciones X-OR, NAND y NOR.

Hay pues un procedimiento sencillo para pasar de una representación por maxterms (minterms) a otra por minterms (maxterms) de la misma función:

1. Me quedo con los números correspondientes a las configuraciones de entrada donde la función es *uno*. Así obtengo la representación por minterms de esa función.

- 2. Me quedo con la lista de los números donde la función es *cero*. Así obtengo se representación por maxterms.

- 3. Uso las expresiones correspondientes a ambas representaciones y compruebo, usando los teoremas y postulados de álgebra de Boole, que ambas representaciones coinciden. Así, para los cuatro ejemplos del ejercicio anterior tendríamos:

Caso a) minterms (0 y 3) y maxterms (1,2):

$$f_m^a = m_0 + m_3 = \bar{x}_1 \bar{x}_2 + x_1 x_2 \tag{1.20}$$

$$f_M^a = M_1 + M_2 = (x_1 + \bar{x}_2)(\bar{x}_1 + x_2)$$

[1.21]

desarrollando  $f_M^a$ , tenemos:

$$(x_1 + \overline{x_2})(\overline{x_1} + x_2) = x_1 \overline{x_1} + x_1 x_2 + \overline{x_2} \overline{x_1} + x_2 \overline{x_2} = x_1 x_2 + \overline{x_2} \overline{x_1}$$

[1.22]

que es la misma expresión obtenida con minterms.

**Ejercicio.** Comprobar ahora que en los casos b, c y d también se trata de la misma función desarrollando la expresión por maxterms y simplificándola.

Solución

Caso b)

$$f_m^b = \bar{x}_1 x_2 + x_1 \bar{x}_2$$

[1.23]

$$f_{M}^{b} = (x_{1} + x_{2})(\bar{x}_{1} + \bar{x}_{2}) = x_{1}\bar{x}_{1} + x_{1}\bar{x}_{2} + x_{2}\bar{x}_{1} + x_{2}\bar{x}_{2} = x_{1}\bar{x}_{2} + x_{2}\bar{x}_{1}$$

[1.24]

Caso c)

$$f_m^c = \bar{x_1}\bar{x_2} + \bar{x_1}x_2 + \bar{x_1}\bar{x_2} = \bar{x_1}(\bar{x_2} + x_2) + \bar{x_2}(\bar{x_1} + x_1) = \bar{x_1} + \bar{x_2}$$

[1.25]

$$f_M^c = \left(\overline{x}_1 + \overline{x}_2\right) \tag{1.26}$$

Caso **d**)

$$f_m^d = \bar{x}_1 \bar{x}_2$$

[1.27]

$$f_M^d = (x_1 + \bar{x}_2)(\bar{x}_1 + x_2)(\bar{x}_1 + \bar{x}_2) = (x_1 x_2 + \bar{x}_1 \bar{x}_2)(\bar{x}_1 + \bar{x}_2) = \bar{x}_1 \bar{x}_2$$

[1.28]

La expresión de cada maxterm,  $M_j$ , se obtiene de complementar la expresión del minterm de igual subíndice. Es decir,

$$M_{j} = \overline{m}_{j}$$

y  $m_{j} = \overline{M}_{j}$  para  $i = 0,1,...,2^{n-1}$  [1.29]

lo que es fácil de demostrar usando dos veces los teoremas de DeMorgan. Esto nos lleva a la relación global entre las dos formas de representación para una misma función, f:

forma minterm de

$$f = forma maxterm de f$$

[1.30]

forma maxterm de

$$f = f$$

[1.31]

El que aparezca  $\overline{f}$  en vez de f en estas expresiones es lo equivalente a lo que hicimos antes al quedarnos con los ceros de f para obtener los maxterms.

**Ejercicios** (I) Dadas las siguientes funciones de tres variables en representación por minterms, obtener su representación por maxterms

**a)**

$$f_m = \sum m(0,1,2,6,7)$$

**b)**

$$f_m = \sum m(2,3,4,5,6)$$

#### Solución

a) La expresión en minterms de f,  $(f_m)$ , nos da los "1" de f. Busquemos entonces sus ceros que estarán en las líneas complementarias de la tabla de verdad, es decir en (3,4,5). Por consiguiente, podremos escribir directamente que la expresión maxterms de f es:

$$f_M = M_3 M_4 M_5 ag{1.32}$$

También podríamos haber usado la expresión general [1.31] que nos dice que la forma maxterm de f,  $(f_M)$ , es el complemento de la forma minterm de  $\overline{f}$ ,  $(\overline{f_m})$ . Así, el proceso a seguir es:

1) Dado

$$f_m = \sum m(0.1.2.6.7)$$

obtener la forma minterm de  $\overline{f}$ ,  $\overline{f_m} = \sum m(.3.4.5)$

2) Complementarla para obtener la forma maxterm,

$$f_M = \overline{f_m} = \overline{\Sigma m(3,4,5)} = \overline{m_3} \ \overline{m_4} \ \overline{m_5} = M_3 M_4 M_5$$

**b)**

$$f_m = \sum m(2,3,4,5,6)$$

$$\overline{f_m} = \sum m(0,1,7)$$

$$f_M = \overline{f_m} = \overline{\Sigma m(0,1,7)} = \overline{m_0} \ \overline{m_1} \ \overline{m_7} = M_0 M_1 M_7$$

[1.33]

**Ejercicios** (II) Dadas las siguientes funciones  $f_M$  en representación por maxterms, obtener sus representaciones equivalentes usando minterms,  $f_m$ .

a)

$$f_M = M_2 M_3 M_4 M_5 M_6$$

**b)**

$$f_M = M_0 M_1 M_2 M_6 M_7$$

#### Solución

De forma dual a como razonamos en el ejercicio anterior, la expresión en maxterms de f,  $(f_M)$ , nos da los ceros de f. Busquemos entonces sus unos que estarán en las líneas complementarias de la tabla de verdad, es decir en (0, 1, 7). Por consiguiente, podemos escribir directamente que la expresión en minterm de f,  $(f_m)$ , será:

$$f_m = m_0 + m_1 + m_7 \tag{1.34}$$

También podríamos haber usado la expresión general [1.30] que nos dice que la forma minterm de f,  $(f_m)$ , es el complemento de la forma maxterm de  $\overline{f}$ . Así, los pasos a seguir son:

- 1) Dado  $f_M = \prod M(2,3,4,5,6)$ , obtener la forma maxterm de  $\overline{f}$ ,  $\overline{f_M} = \prod M(0,1,7)$ .

- 2) Complementarla

$$f_m = \overline{f_M} = \overline{\Pi M(0, 1, 7)} = \overline{M_0} + \overline{M_1} + \overline{M_7} = m_0 + m_1 + m_7$$

Análogamente razonaríamos en el caso b):

$$f_m = \overline{f_M} = \overline{\Pi M(3,4,5)} = \overline{M_3} + \overline{M_4} + \overline{M_5} = m_3 + m_4 + m_5$$

[1.35]

Conviene recordar que siempre que tengamos dudas sobre si nuestra conversión de minterms a maxterms o viceversa, es o no es correcta, podemos pasar a la representación en términos de las

variables reales,  $x_1$ ,  $x_2$ ,  $x_3$ , donde ambas representaciones deben coincidir, como vimos en las ecuaciones [1.20] a [1.28] del ejercicio anterior.

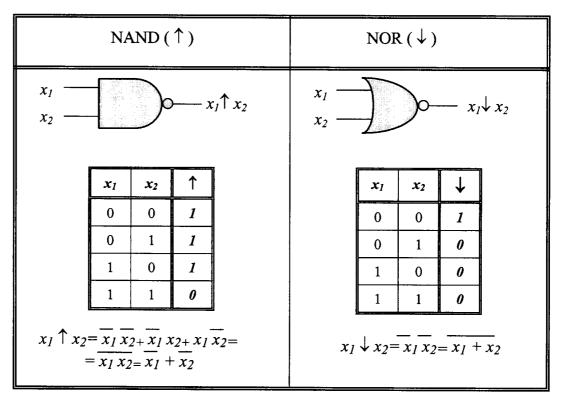

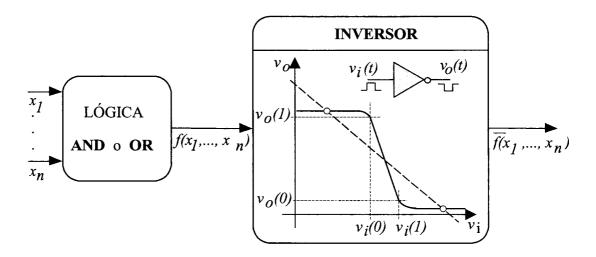

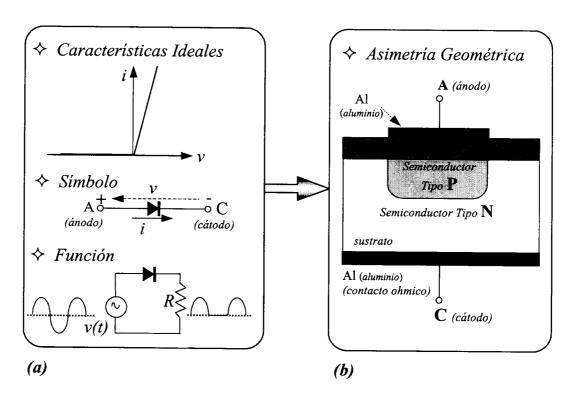

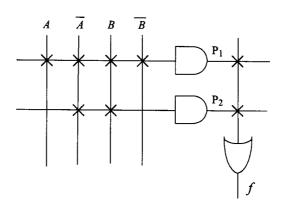

# 1.5. OTRAS REPRESENTACIONES COMPLETAS (NAND, NOR)

Tanto en la suma de productos como en el producto de sumas, para sintetizar cualquier función sólo necesitamos la realización electrónica de tres operadores: AND, OR y NO. Por eso decimos que estos tres operadores constituyen un conjunto completo. Existen, sin embargo otros conjuntos completos más pequeños y, por consiguiente, más útiles a la hora de realizarlos físicamente. Nos referimos a los circuitos NAND (AND seguido de inversor) y NOR (OR seguido de inversor). Con cualquiera de ellos se puede sintetizar cualquier función lógica. Nos vamos acercando así al objetivo de este tema que es definir las exigencias computacionales mínimas del tratamiento digital de la información. Digámoslo ya avanzando conocimientos. El propósito de la Electrónica Digital es obtener realizaciones físicas en tecnología bipolar o unipolar de conjuntos completos de operadores lógicos. Con ellos podremos sintetizar cualquier función combinacional (de codificación aritméticológica o de ruta de datos) y con leves modificaciones, cualquier función secuencial. Razones adicionales sobre facilidad de fabricación harán que sea ventajosa la representación mediante un único operador, NAND ó NOR. Así, todo lo que necesitamos es una suma o un producto seguidos de un inversor.

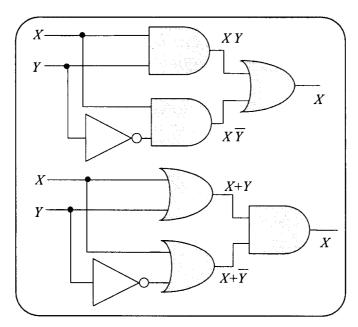

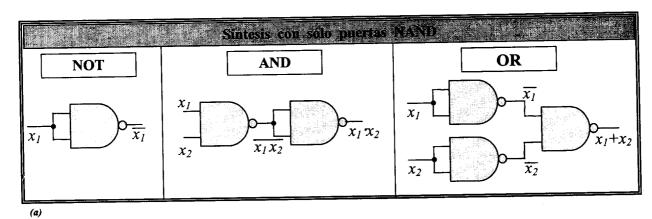

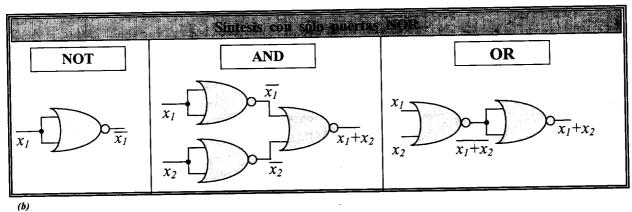

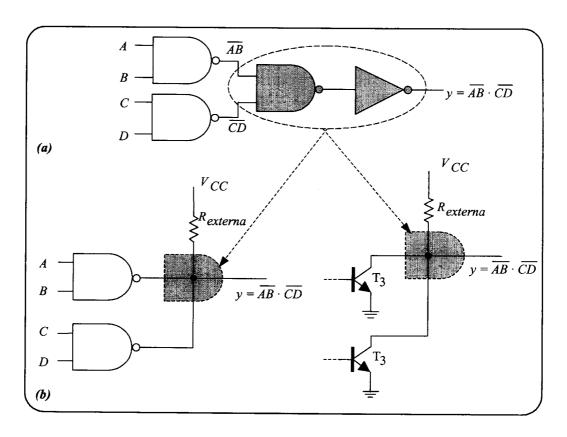

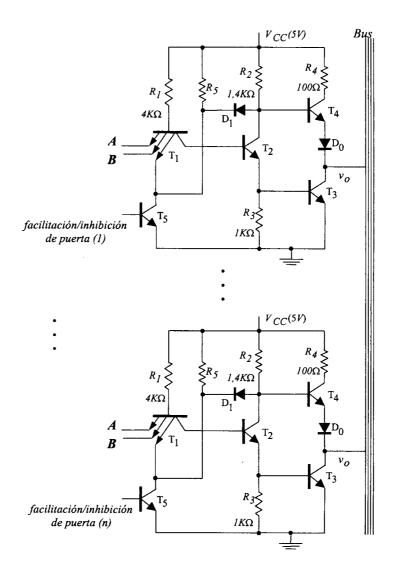

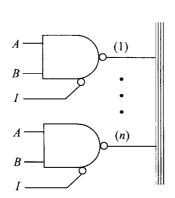

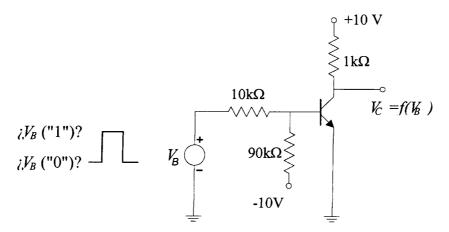

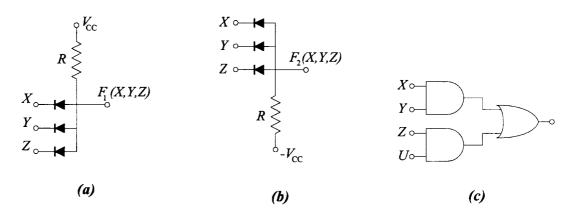

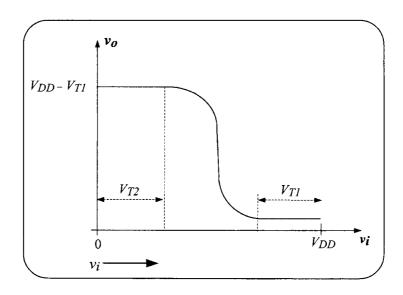

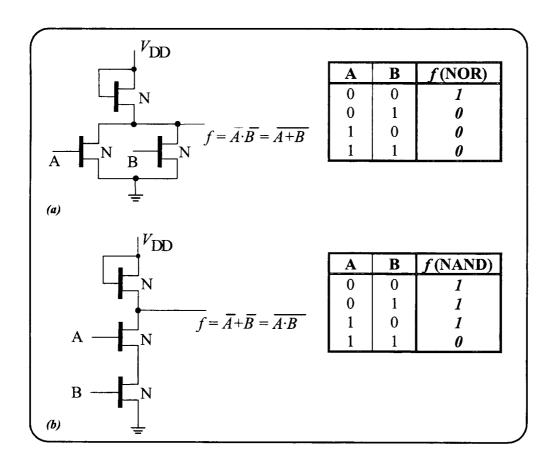

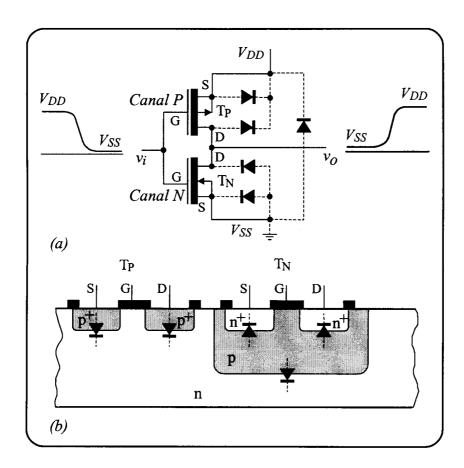

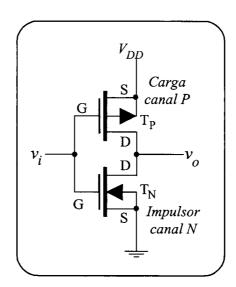

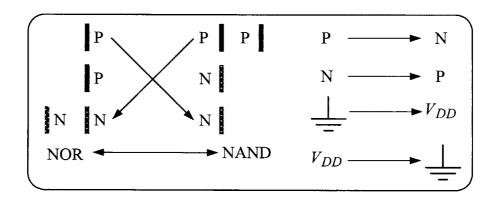

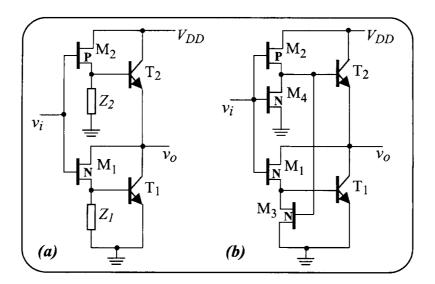

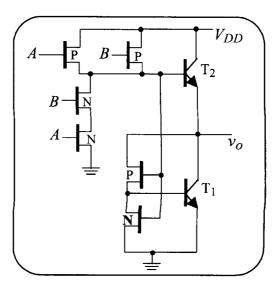

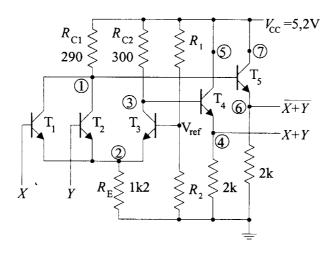

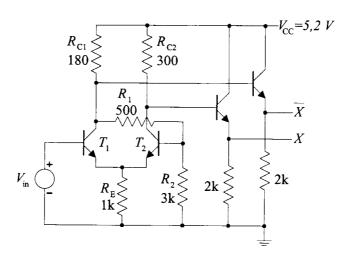

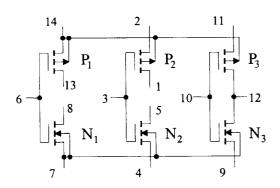

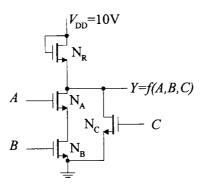

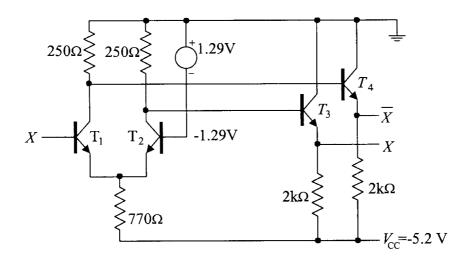

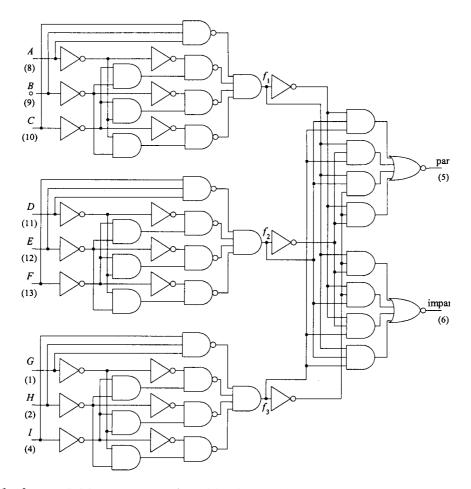

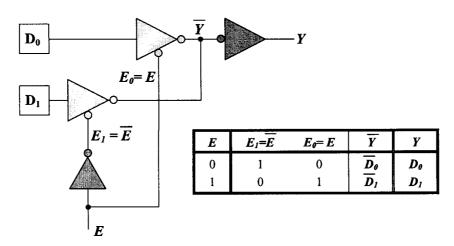

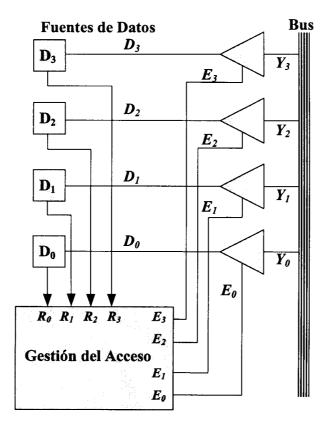

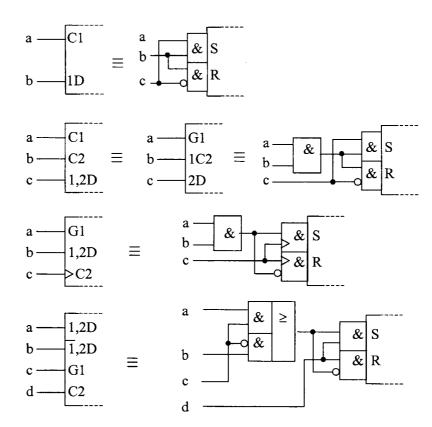

La figura 1.21 incluye las tablas de verdad, los símbolos y las expresiones de los operadores NAND y NOR. Como muestra de su complitud se ilustra también en la figura 1.22 la síntesis de los operadores del anterior conjunto completo (AND, OR y complemento) en términos de sólo operadores NAND y sólo operadores NOR.

De forma general, aplicando los teoremas de DeMorgan a la forma normal disyuntiva, podemos obtener las expresiones equivalentes en NAND y NOR. Veamos el caso NAND:

$$f = \sum_{i} a_{i} \cdot m_{i} \tag{1.36}$$

Si complementamos ahora dos veces obtenemos:

$$f = \overline{f} = \sum_{i} (a_i m_i) = \prod_{i} (\overline{a_i m_i})$$

NAND de (NAND de  $a_i$  y  $m_i$ )

NAND de (NAND de  $a_i$  y  $m_i$ )

Con lo que ya tenemos la expresión de f usando dos niveles de puertas NAND. En el primer nivel obtenemos el NAND de  $a_i$  y  $m_i$ . En un segundo nivel obtenemos el NAND de las expresiones anteriores. Si llamamos  $P_i$  a la negación de los productos  $a_i m_i$  (su NAND) podemos volver a escribir la expresión anterior de la forma:

$$f = \overline{f} = \overline{\sum_{i} (a_{i} m_{i})} = \overline{\prod_{i} (a_{i} m_{i})} = \overline{\prod_{i} P_{i}} = (a_{0} \uparrow m_{0}) \uparrow (a_{1} \uparrow m_{1}) \uparrow \dots \uparrow (a_{2^{n}-1} \uparrow m_{2^{n}-1})$$

$$P_{i} \qquad \qquad NAND de P_{i}$$

Figura 1.21. Definición de los operadores NAND y NOR.

Figura 1.22. Síntesis del conjunto completo (AND, OR, NOT). (a) Usando sólo operadores NAND. (b) Usando sólo operadores NOR.

Por ejemplo, para  $f = x_1 + x_2$  tendremos:

$$\overline{f} = \overline{x_1 + x_2} = \overline{x_1} \cdot \overline{x_2}$$

[1.39]

$$\overline{\overline{f}} = \overline{x_1 \cdot x_2} = f \tag{1.40}$$

donde  $\bar{x}_1$  es el NAND de  $x_1$  consigo misma,  $\bar{x}_2$  el NAND de  $x_2$  consigo misma y, finalmente un nuevo NAND con los resultados anteriores. El circuito correspondiente es el que se ilustra en la figura 1.22. Análogamente obtendríamos el correspondiente al producto  $x_1 \cdot x_2$ .

$$f = x_1 \cdot x_2 \tag{1.41}$$

$$\overline{f} = \overline{x_1 \cdot x_2}$$

[1.42]

Ahora que hemos visto de forma individual los distintos tipos de representación es hora de comprobar con algunos ejemplos lo que hemos aprendido.

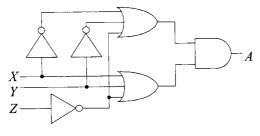

Ejercicio: Representar con sólo puertas NAND la siguiente función:

$$A = XY\overline{Z} + XYZ + X(Y + \overline{Z})$$

Para el paso a NAND podemos usar el siguiente procedimiento general:

- 1. *Obtener una expresión mínima* en forma de suma de productos (este apartado lo veremos al comentar el **objetivo 6**).

- 2. *Complementar dos veces*. Al complementar dos veces hemos dejado la función como estaba, por lo que siempre podremos hacerlo.

- **3.** *Aplicar los teoremas de De Morgan*. La aplicación repetida de los Teoremas de De Morgan debe pararse cuando:

- a) Sólo encontramos variables negadas  $(\overline{X}, \overline{Y})$  que se sintetizan con un inversor, el cual es un caso particular de una puerta NAND en la que se unen las dos entradas.

- b) Sólo encontramos negaciones de productos  $(X\overline{Y}, \overline{X}Y, ...)$ .

### Solución:

De acuerdo con el procedimiento descrito, primero complementamos dos veces. Así,

$$A = \overline{\overline{A}} = XY\overline{Z} + XYZ + X(Y + \overline{Z}) = \overline{XY\overline{Z} + XYZ + XY + X\overline{Z}}$$

[1.43]

A continuación aplicaremos los teoremas de DeMorgan, resultando:

$$A = \overline{XYZ} + \overline{XYZ} + \overline{XYZ} + \overline{XZ} = \overline{XYZ} \overline{X$$

Por último, comprobaremos con la tabla de verdad que ambas representaciones [1.43] y [1.44] coinciden.

| X | Y | Z | $XY\overline{Z}$ | XYZ | $X(Y+\overline{Z})$ | A [1.43] | $\overline{XY\overline{Z}}$ | XYZ | XY | $\overline{X\overline{Z}}$ | A [1.44] |

|---|---|---|------------------|-----|---------------------|----------|-----------------------------|-----|----|----------------------------|----------|

| 0 | 0 | 0 | 0                | 0   | 0                   | 0        | 1                           | 1   | 1  | 1                          | 0        |

| 0 | 0 | 1 | 0                | 0   | 0                   | 0        | 1                           | 1   | 1  | 1                          | 0        |

| 0 | 1 | 0 | 0                | 0   | 0                   | 0        | 1                           | 1   | 1  | 1                          | 0        |

| 0 | 1 | 1 | 0                | 0   | 0                   | 0        | 1                           | 1   | 1  | 1                          | 0        |

| 1 | 0 | 0 | 0                | 0   | 1                   | 1        | 1                           | 1   | 1  | 0                          | 1        |

| 1 | 0 | 1 | 0                | 0   | 0                   | 0        | 1                           | 1   | 1  | 1                          | 0        |

| 1 | 1 | 0 | 1                | 0   | 1                   | 1        | 0                           | 1   | 0  | 0                          | 1        |

| 1 | 1 | 1 | 0                | 1   | 1                   | 1        | 1                           | 0   | 0  | 1                          | 1        |

Figura 1.23. Tabla de verdad para demostrar que las expresiones [1.43] y [1.44] coinciden.

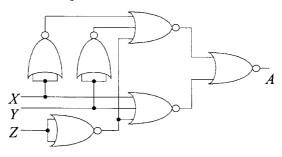

Ejercicio: Pasar de NAND a NOR la siguiente función:

$$A = f(X,Y,Z) = \overline{X} \overline{Y}Z + \overline{X}YZ$$

### Solución

Para el paso de NAND a NOR, también es fácil comprobar el grado de comprensión alcanzado usando el siguiente procedimiento general que describimos sobre un ejemplo:

1. Partimos de una expresión que sólo usa puertsa NAND, por ejemplo

$$A = f(X, Y, Z) = \overline{X} \overline{Y} Z + X \overline{Y} Z$$

[1.45]

2. Aplicamos DeMorgan:

$$A = \overline{\overline{X} \ \overline{Y} \ Z + X \ Y \ Z} = \left(X + Y + \overline{Z}\right) \left(\overline{X} + \overline{Y} + \overline{Z}\right)$$

[1.46]

3. Dibujamos el circuito correspondiente en la lógica de dos niveles (OR-AND)

Figura 1.24. Implementación de la función A con inversores y puertas AND y OR

**4.** Negamos dos veces y aplicamos de nuevo DeMorgan para obtener la representación con sólo puertas NOR

$$A = \overline{\left(\overline{X + Y + \overline{Z}}\right)\left(\overline{X} + \overline{Y} + \overline{Z}\right)} = \overline{\left(\overline{X + Y + \overline{Z}}\right) + \overline{\left(\overline{X} + \overline{Y} + \overline{Z}\right)}}$$

[1.47]

5. Representamos el circuito correspondiente:

Figura 1.25. Implementación de la función A con sólo puertas NOR

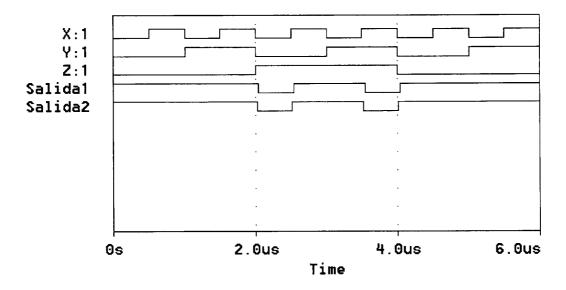

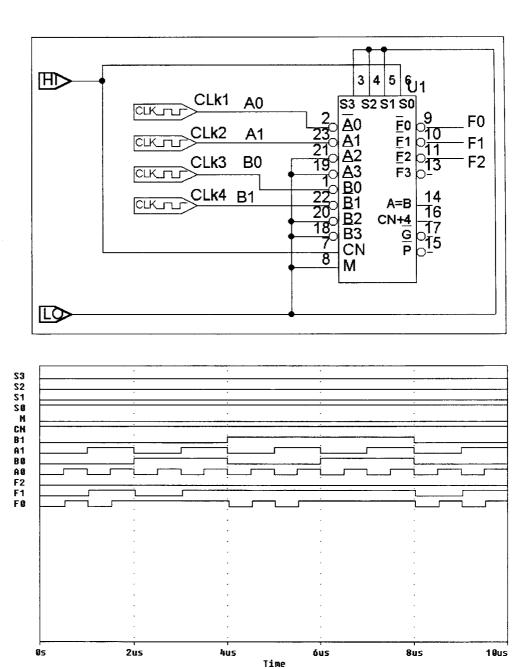

6. Usamos el simulador para comprobar que ambos circuitos se comportan igual

Dado que en la versión reducida y de uso libre del simulador PSpice no contamos con puertas OR de 3 entradas hemos usado las de 2 entradas, realizando las funciones OR de tres variable en dos etapas. En una primera etapa hacemos la función OR de dos variables y en la siguiente etapa hacemos la función OR de la tercera variable con el resultado de la primera etapa.

Figura 1.26. Implementación de la función A con el simulador PSpice.

Figura 1.27 Resultado de la simulación y comprobación de la validez de ambos diseños.

Como puede observarse en el cronograma las dos salidas coinciden para las ocho configuraciones de entrada.

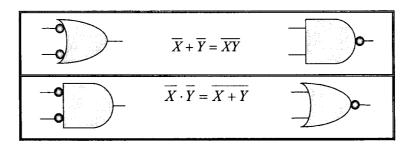

Una forma más sencilla y rápida de conseguir la transformación, en los casos en los que disponemos del circuito en su representación OR-AND, es emplear un método gráfico, consistente en negar las salidas de las puertas del primer nivel y las entradas de las puertas del segundo nivel. Con esta doble negación, que no altera lo más mínimo la función del circuito, se convierten las puertas AND (OR) del primer nivel en puertas NAND (NOR) y las puertas OR (AND) del segundo nivel en puertas OR (AND) con las entradas negadas, o lo que es lo mismo en puertas NAND (NOR) con las entradas sin negar (figura 1.28). Estos cambios, no son más que el resultado de la aplicación directa de la representación gráfica de los teoremas de DeMorgan.

Este método es igualmente válido para obtener la representación sólo con puertas NAND partiendo del esquema del circuito representado con la lógica de dos niveles AND-OR (suma de minterms), como para obtener la representación sólo con puertas NOR a partir del esquema del circuito representado con la lógica de dos niveles OR-AND (producto de maxterms)

Figura 1.28. Implementación de los teoremas de DeMorgan

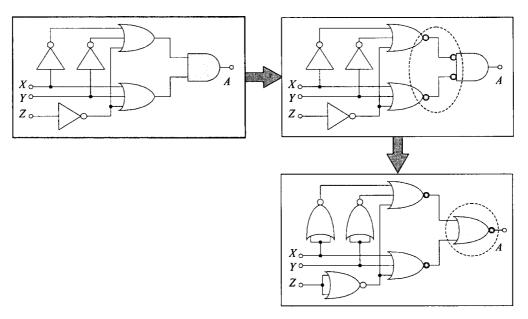

Ejercicio: Aplicar el método gráfico descrito anteriormente al circuito del ejercicio anterior:

### Solución

La *figura 1.29* muestra los pasos sucesivos para pasar un circuito implementado con inversores, puertas OR y AND a su implementación con sólo puertas NOR. Para ello, primero hemos aplicado el método gráfico para el paso de OR-AND a sólo NOR y después hemos sustituido los inversores por puertas NOR con las entradas unidas.

Figura 1.29. Ilustración del método gráfico.

# 1.6. ANÁLISIS Y SÍNTESIS

Vamos a ver de forma sencilla y a través de ejemplos en que consisten los procesos de *análisis* y *síntesis* de circuitos lógicos.

Analizar un circuito lógico es encontrar la función lógica que calcula, a partir del esquema de conexión de las variables de entrada con los distintos operadores hasta llegar a la variable de salida.

La variable o variables dependientes (la función) se encuentra a la salida de la última puerta y, por consiguiente, para obtener la expresión lógica que la conecta con las entradas basta seguir el camino de las variables de entrada hasta llegar a la salida y comprobar por inducción completa que ambos (circuito y expresión lógica) coinciden porque poseen la misma tabla de verdad. Los problemas E.1.1 y E.1.2 resueltos en el texto de problemas son representativos de este procedimiento.

Aquí, en el primer tema dedicado a los circuitos lógicos combinacionales de pocas variables, el problema de análisis es realmente sencillo. Veremos más adelante, al estudiar circuitos secuenciales, cómo no es tan sencillo "descubrir" la función global que realizan a partir de las conexiones entre sus componentes. La clave está en el concepto de "estado" y en la existencia de lazos de realimentación. Aprovechémonos de momento de la sencillez del análisis en lógica combinacional, obteniendo la función lógica que realizan los circuitos de los dos ejercicios siguientes en los que hemos ido señalando las distintas transformaciones que sufren las variables de entrada, A, B y C hasta llegar a las funciones  $F_1$ ,  $F_2$  y  $F_3$ .

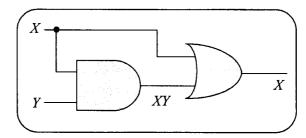

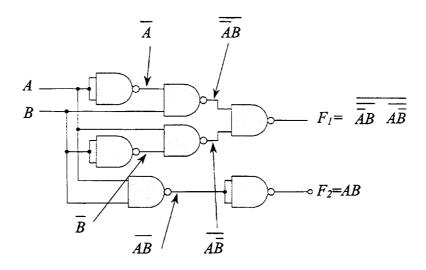

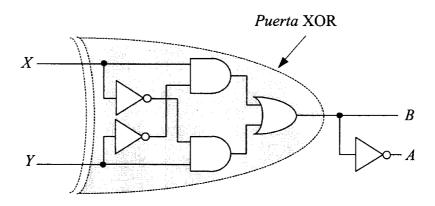

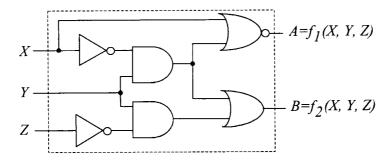

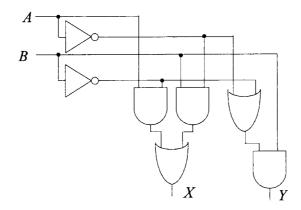

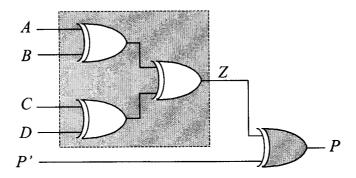

**Ejercicio:** Analizar el circuito de la figura corresponde a una función múltiple  $(F_1, F_2)$  de dos variables  $(A \ y \ B)$ .

### Solución:

La forma de analizar un circuito es seguir el camino de la señal desde las entradas, A y B, hasta las salidas,  $F_1$  y  $F_2$ , anotando las transformaciones que introducen los operadores que se encuentran en el camino.

Figura 1.30.

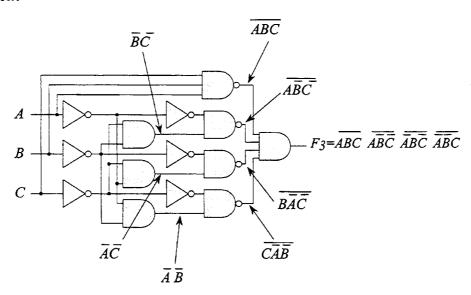

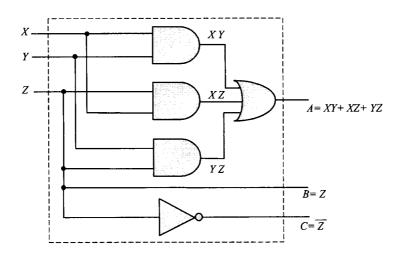

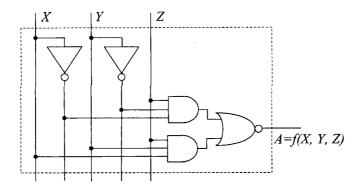

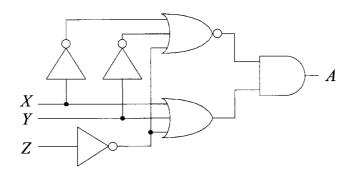

Ejercicio: Repetir el procedimiento de análisis para el circuito de la figura 1.31.

## Solución:

Figura 1.31.

Las dos fases esenciales en todo proceso de síntesis son:

Fase a: Paso de una descripción en lenguaje natural a una función lógica.

Fase b: Paso de una función lógica a su circuito correspondiente.

Veamos ahora algunos ejemplos de ambas fases.

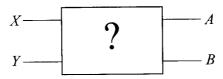

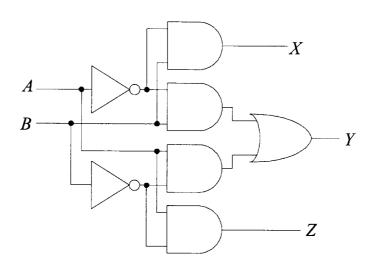

Ejercicio: Obtener una descripción lógica, incluyendo la selección de variables de entrada y salida, de un circuito con dos entradas y dos salidas tal que la primera salida esté en alta cuando el valor en las dos entradas es el mismo y la segunda salida está en alta cuando no coinciden las entradas. Obtener también el circuito que implementa dichas funciones

### Solución:

Fase a: Paso de una descripción en lenguaje natural a una función lógica.

1. Empezamos asignando dos variables (X,Y) a las entradas y otras dos (A,B) a las salidas.

2. Construimos una tabla de verdad en la que describimos las cuatro configuraciones lógicas posibles en la entrada y ponemos un uno en los términos mínimos que hacen pasar A a alta y en otra columna, los que hacen pasar B a alta.

| X | Y | A | В |

|---|---|---|---|

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Figura 1.32. Tabla de verdad

Si hacemos la síntesis usando los términos mínimos tomamos las configuraciones de entrada que hacen que la salida sea 1. Así, para la función A, tenemos:

$$A = \overline{X} \ \overline{Y} + X \ Y \tag{1.48}$$

Análogamente para la salida obtenemos:

$$B = \overline{X} Y + X \overline{Y}$$

[1.49]

Es decir, la función A es la coincidencia y la B la anticoincidencia ó OR exclusivo.

Así,

$$A = \overline{X \oplus Y}$$

$y$   $B = X \oplus Y$  [1.50]

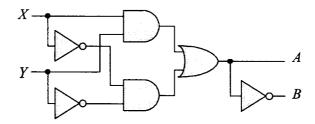

Fase b: Paso de una función lógica a su circuito correspondiente.

Figura 1.33.

Como puede observarse esta no es la única forma de implementar estas funciones. En este caso hemos hecho el circuito para la función A y después, negando la salida, hemos obtenido la función B. De igual forma, es correcta la implementación si hacemos el circuito que implementa la función B y después complementando su salida obtenemos la función A. Así:

Figura 1.34.

**Ejercicio:** Diseñar y minimizar un circuito lógico de tres variables de entrada y tres de salida de forma que responda a cada una de las siguientes condiciones:

- a) Dos o más de las entradas estén en alta a la vez.

- b) El decimal equivalente al número binario que representan las tres entradas sea impar (1, 3, 5 \u00f3 7).

- c) El decimal equivalente al número binario que representan las tres entradas sea par (0, 2, 4 ó 6).

### Solución:

Fase a: Paso de una descripción en lenguaje natural a una función lógica.

1. Empezamos asignando tres variables (X, Y, Z) a las entradas y otras tres (A, B, C) a las salidas.

2. Construimos la tabla de verdad. Para ello en la primera columna ponemos los números decimales de 0 a 7, ya que con tres variables podremos representar 2<sup>3</sup> = 8 configuraciones de entrada. Las tres columnas siguientes son las entradas y las siguientes columnas son las tres salidas que nos piden en el problema y que se corresponden con las soluciones a los apartados a, b y c del enunciado. Así, la tabla de verdad es:

| N°<br>Decimal | X | Y | Z      | Dos o mas entradas<br>en Alta<br>A        | N° decimal impar<br>B | N° decimal par<br>C |

|---------------|---|---|--------|-------------------------------------------|-----------------------|---------------------|

| 0             | 0 | 0 | 0      | 0                                         | 0                     |                     |

| 2             | 0 | 0 | 0      | 0                                         |                       | <b>0</b>            |

| 3             | 0 | 1 | 1      | <i>i</i> , <i>i</i> , ,                   |                       | 0                   |

| 5             | 1 | 0 | 0<br>1 |                                           |                       | <b>1</b>            |

| 6             | 1 | 1 | 0      |                                           | 0                     | 1                   |

| 7             | 1 | 1 | 1      | $A = A \boldsymbol{J} + A \boldsymbol{J}$ |                       | 0                   |

Figura 1.35.

Ahora vemos cuáles son las configuraciones de entrada que producen un 1 en las distintas salidas. Es decir, vemos qué términos mínimos participan en la producción de cada salida. Así,

$$A = \overline{X} YZ + X \overline{Y} Z + X Y \overline{Z} + X Y Z$$

[1.51]

$$B = \overline{X} \, \overline{Y} Z + \overline{X} Y Z + X \overline{Y} Z + X Y Z \tag{1.52}$$

$$C = \overline{X} \overline{Y} \overline{Z} + \overline{X} \overline{Y} \overline{Z} + X \overline{Y} \overline{Z} + X \overline{Y} \overline{Z} + X \overline{Y} \overline{Z}$$

[1.53]

Aunque veremos más adelante la minimización por mapas de Karnaugh dentro del Objetivo 6, aquí utilizaremos la aplicación directa de los teoremas y postulados del Algebra de Boole para simplificar estos sencillos ejemplos de síntesis.

$$A = \overline{X}YZ + X\overline{Y}Z + XY\overline{Z} + XYZ = YZ(X + \overline{X}) + XY(Z + \overline{Z}) + XZ(Y + \overline{Y}) = YZ + XY + XZ$$

[1.54]

Análogamente:

$$B = \overline{X} \, \overline{Y} Z + \overline{X} \, Y Z + X \overline{Y} Z + X Y Z = \overline{Y} Z \Big( X + \overline{X} \Big) + Y Z \Big( X + \overline{X} \Big) = \overline{Y} Z + Y Z = Z \Big( Y + \overline{Y} \Big) = Z$$

$$C = \overline{X} \, \overline{Y} \, \overline{Z} + \overline{X} \, Y \, \overline{Z} + X \overline{Y} \, \overline{Z} + X Y \, \overline{Z} = \overline{Y} \, \overline{Z} \Big( X + \overline{X} \Big) + Y \overline{Z} \Big( X + \overline{X} \Big) = \overline{Y} \, \overline{Z} + Y \overline{Z} = \overline{Z} \Big( Y + \overline{Y} \Big) = \overline{Z}$$

En estos dos últimos casos podemos llegar a la solución por simple inspección de la tabla de verdad, ya que si comparamos la columna B con las de las variables de entrada observamos que coincide con la columna correspondiente a la entrada Z. Por tanto B=Z. Análogamente los valores de la salida C coincide con los valores complementados de la columna corrrespondiente a la entrada Z. Por tanto  $B=\overline{Z}$ . Sin embargo esto no suele ocurrir en la mayoría de los casos por lo que en general hay que seguir los pasos de alguno de los procedimientos de minimización.

Fase b: Implementación. Paso de una función lógica a su circuito correspondiente.

En esta fase, evidentemente, podemos usar cualquiera de las formas completas (AND, OR, NOT: sólo NAND o sólo NOR) que ya conocemos. Así, en el primer caso obtendríamos un circuito como el que se ilustra en la *figura 1.36*.

Figura 1.36.

# 1.7 Introducción a la Minimización

Minimizar una función lógica es obtener la expresión más simplificada posible para la misma de forma que el número de operadores necesarios para su síntesis es también mínimo.

Un tratamiento adecuado de este problema queda fuera del alcance de este tema de introducción a la electrónica digital, por lo que sólo presentaremos los conceptos mínimos necesarios para comprender los procedimientos de síntesis de las funciones combinacionales y secuenciales que estudiaremos más adelante.

Si pensamos en términos de *suma de productos* parece intuitivo afirmar que una función está en su forma mínima cuando es mínimo el número de productos y, a igualdad de productos, cuando es mínimo el número de variables. Desde un punto de vista algebraico y para pocas variables, el uso directo de algunos postulados y teoremas del álgebra de Boole es suficiente para conseguir la minimización. Por ejemplo,

$$x_1 x_2 + x_1 x_2 = x_1 (x_2 + x_2) = x_1$$

[1.55]

$$x_1 + x_1 x_2 = x_1 (x_2 + 1) = x_1$$

[1.56]

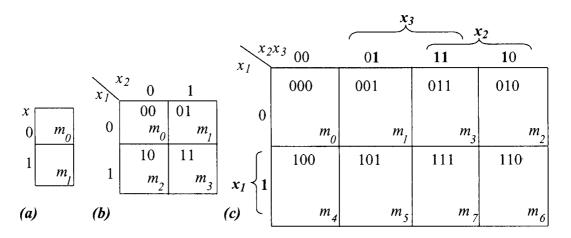

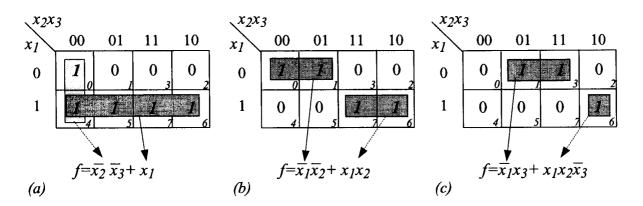

Cada término mínimo posee dos vecinos de los que sólo le diferencia el estado de una variable que en un caso está complementada y en otro sin complementar de forma que si aparecen juntos en una expresión se puede sacar factor común y eliminar la variable que cambia. Los cuatro términos mínimos para dos variables son  $\overline{x_1} \, \overline{x_2}$ ,  $\overline{x_1} \, x_2$ ,  $\overline{x_1} \, x_2$ ,  $\overline{x_1} \, x_2$ ,  $\overline{x_1} \, x_2$ . Así, para el primer término,  $\overline{x_1} \, \overline{x_2}$  tenemos dos vecinos:  $\overline{x_1} \, x_2$  (cambia sólo  $x_2$ ), y  $\overline{x_1} \, \overline{x_2}$  (cambia sólo  $x_1$ ), con lo que podríamos obtener las siguientes simplificaciones: